Other Parts Discussed in Thread: CSD17579Q3A, CSD17577Q5A, CSD17579Q5A, CSD17577Q3A

Dear team

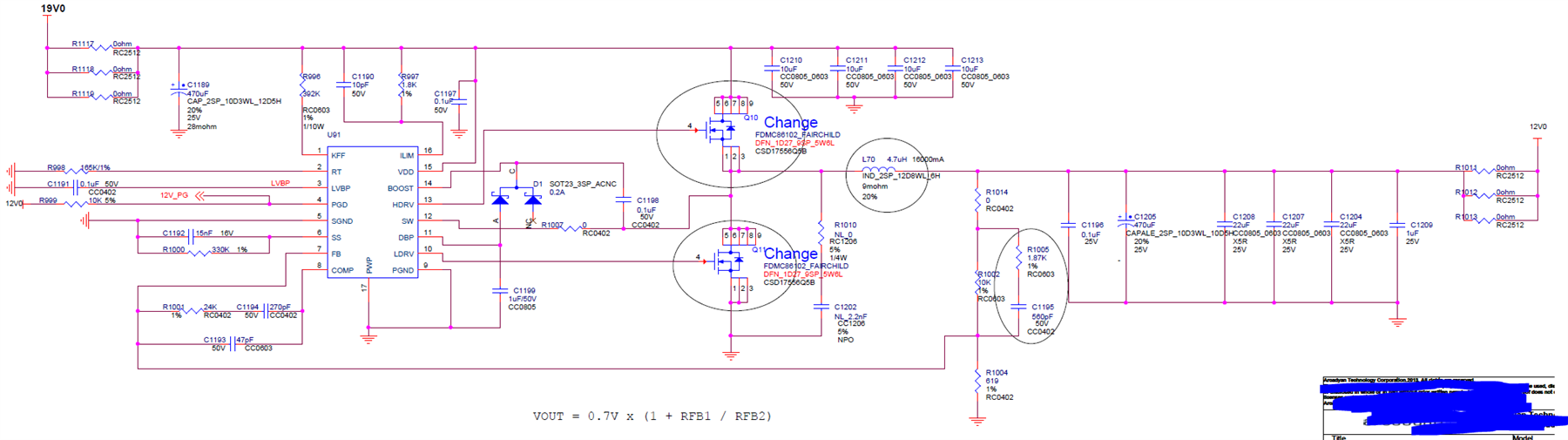

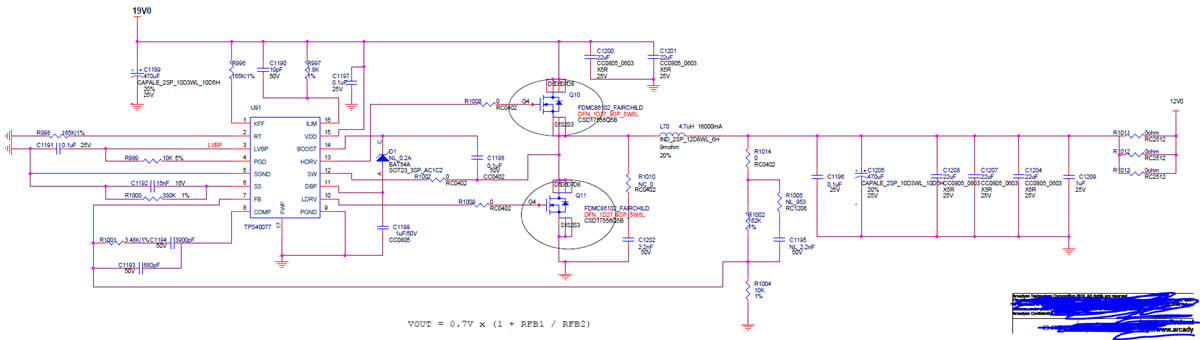

There is a good news that we design in TPS40077 in customer's new project.

The spec is Vin=19V,Vo=12V,Io=12.5A.

Could you help to review the schematic and recommend the solution of Q10 and Q11.

Many thanks

Denny