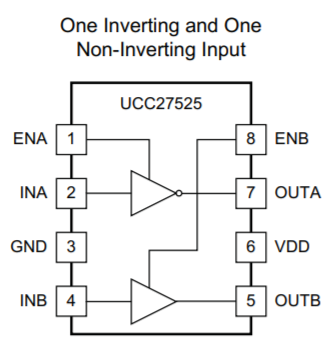

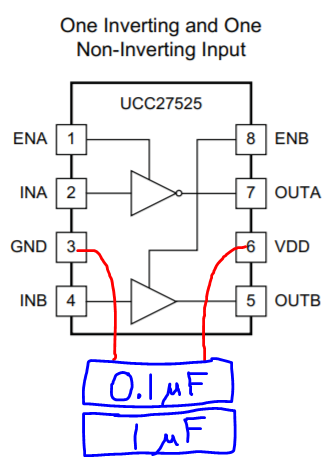

Other Parts Discussed in Thread: UCC27511, CSD18510Q5B, CSD18536KTT, CSD18512Q5B, CSD18563Q5A, CSD19505KTT, CSD19505KCS, UCC27525

Dear Expert,

I can't simulate this circuit in pspice, Is this mosfet circuit is right or not, If wrong kindly help me to built better circuit.

CSD18542KTT