I'm trying to design a buck boost regulator with the LM5175. I need to convert 23-33.6V (8s lithium cells) to stable 24V @ 5A.

I have created schematic and layout, based on LM5175EVM-HD and the excel calculator tool.

Enable resistors are 0 ohm, because I was planning on fitting some resistors afterwards to do UVLO testing. Now EN is tied to VIN with 0 ohm resistor.

Mode resistors are also placed like this to do testing, 100K to gnd is fitted now, which should result in CCM operation with hiccup enabled.

RC snubber values have just been copied from a reference design and must be calculated afterwards (if necessary). They are fitted now as per the schematic.

Here is the schematic:

Here is the board layout. Only top copper is shown since the rest is mostly GND plane. Bottom layer (4 layer board) is used for gate signals and current measurement signals

Here is the test setup:

The circuit is outputting 24V, so that is working. At some input voltages the circuit is stable and I can supply 5A load with 96.5% efficiency. The inductor and mosfets are not the lowest DCR/Rds types so this is fine. Iq is a bit high with 35mA. There are some problems though. I feel like the switching can become unstable depending on input voltage and load current.

What I have observed:

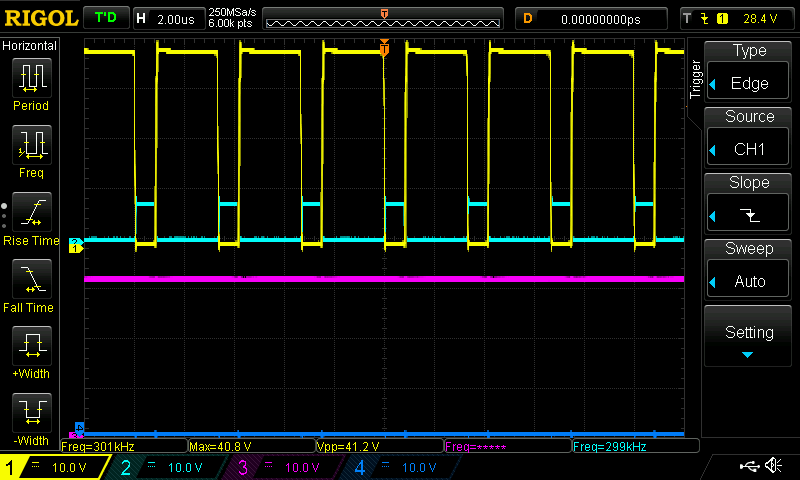

-boost mosfets start switching when well into buck mode (28Vin, 24Vout)

-buck fets start switching when well into boost mode (20V in, 24Vout)

-in some switching cycles the gate drive signals get horrible ringing which is also visible on the SW1/SW2 and Vin/Vout node

-when the above stated condition occurs the Iq of the entire circuit (no load) becomes horrible (>70-150mA).

-with some input voltages the efficiency also dips drastically, making the circuit to dissipate large amounts of heat.

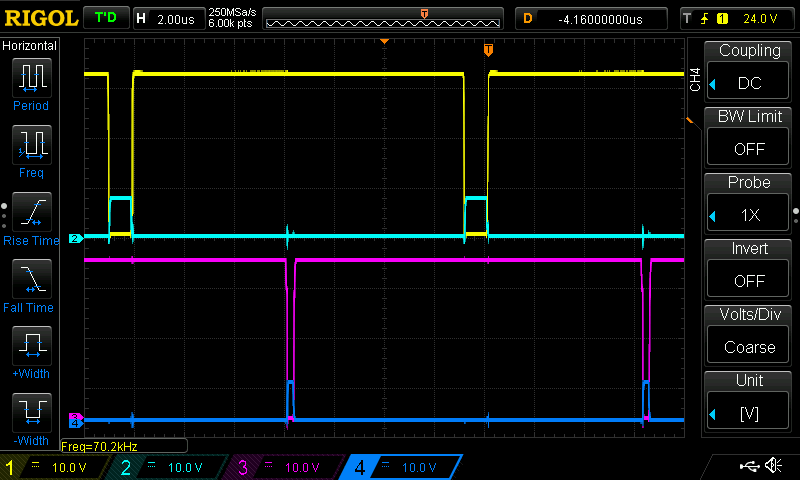

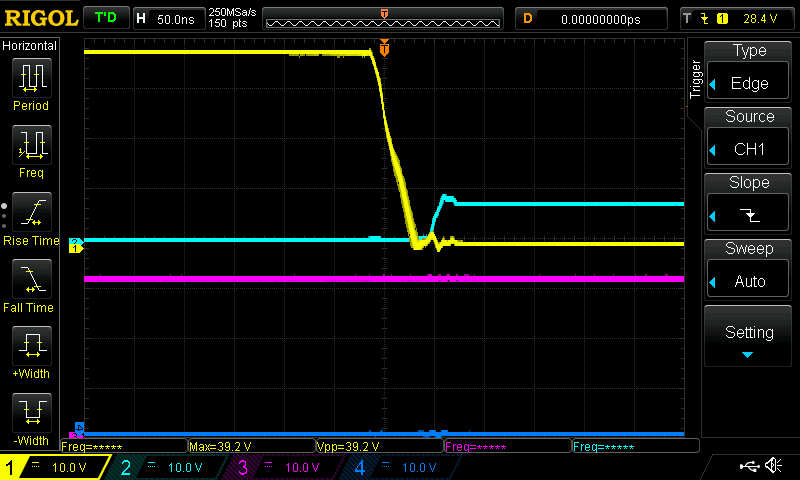

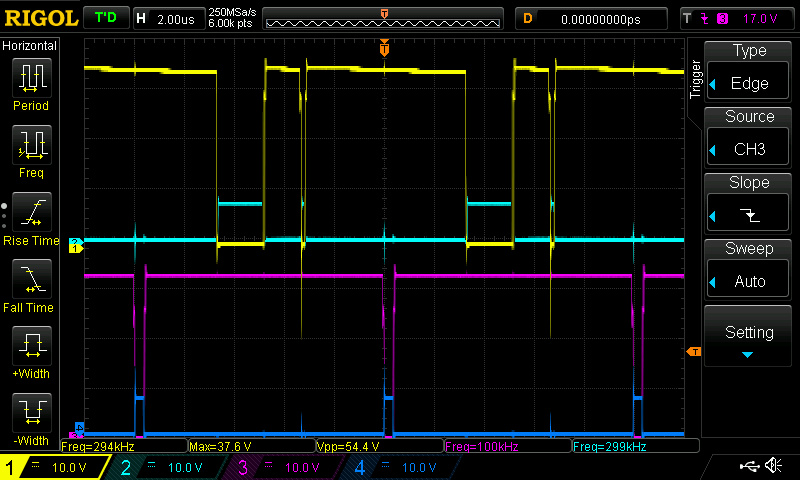

These are the HDRV1 (1), LDRV1 (2), HDRV2 (3) and LDRV2 (4) signals:

at 32Vin the signal is looking pretty nice, and the boost side driver has no activity as expected in buck mode. Iq is 35mA.

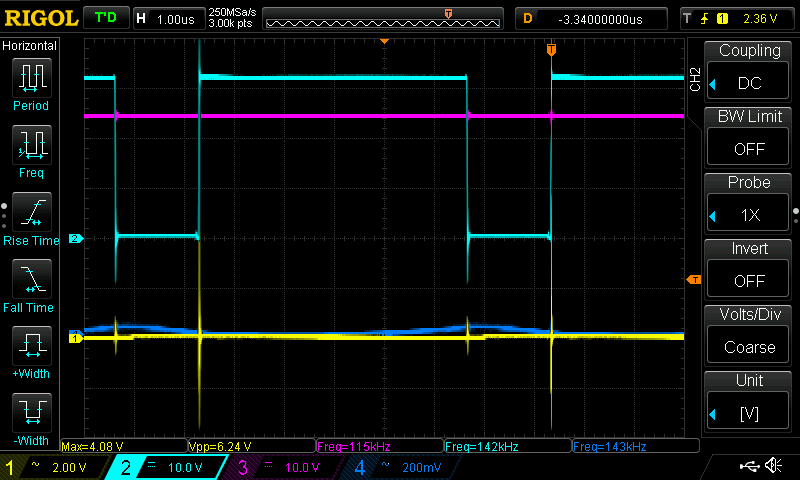

zoomed in HDRV1 and LDRV1 shows nice transition, also good dead time so I assume the fets are not conducting at the same time.

But when the input is reduced to 29V, the driver signals starts looking pretty bad, and the Iq increases to 100mA. Both IC and inductor start heating up.

Also HDRV2 and LDRV2 start switching for some reason:

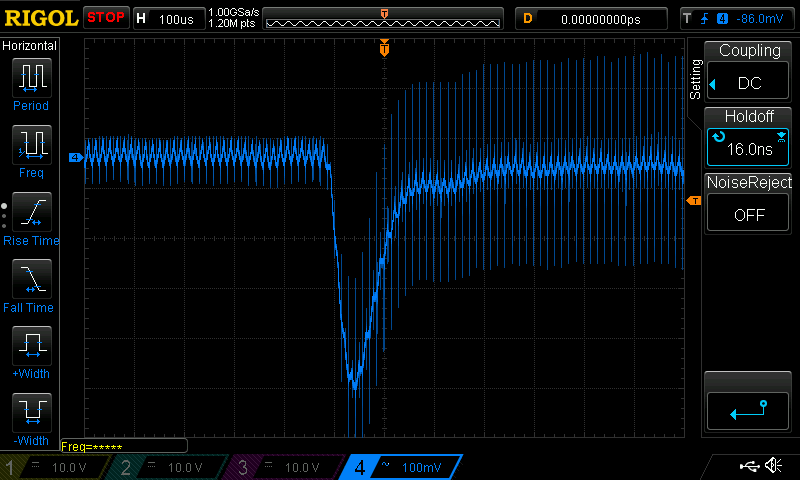

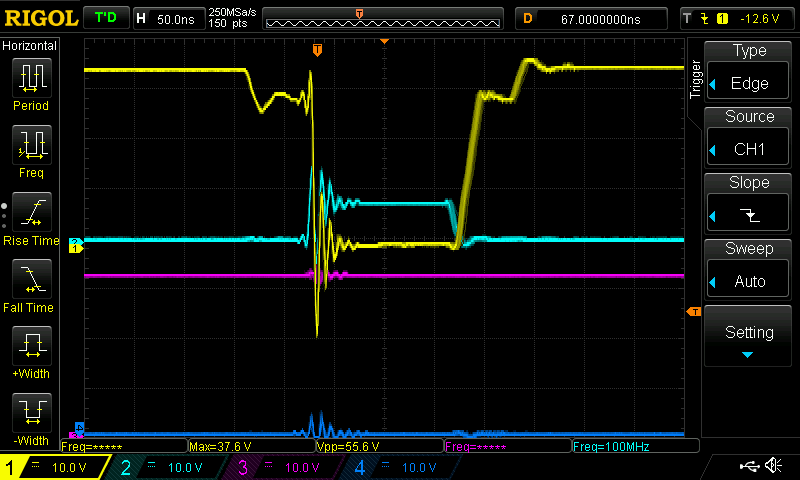

Now zoomed in HDRV1 and LDRV1 shows pretty bad ringing, and to me it seems like both fets are conducting for very short time, like HDRV1 is held by something for a few 10's of ns.

The bad ringing signal also can be seen in HDRV2 and LDR2

I'm no expert with these types of regulators. I can only suspect some kind of instability. The excel calculator shows the following chart with my component values:

comp voltage is measured around 1.6V, so that seems to be alright.

The gate driver signals above are captured with no load at the output. When the instability occurs with a loaded output, the efficiency drops drastically causing the entire thing to heat up quickly.

On a final note, the ringing of the gate signals (4th scope image) is also visible as (or caused by?) quite substantial Vin / Vout ringing (few volts). It won't hurt our application but I doubt that's good for EMI.

Any kind of help or insight as to what might be causing these instabilities would be hugely helpful. Would changing gate resistors and compensation components be a good place to start?

polymer input/output caps: https://nl.mouser.com/datasheet/2/212/1/KEM_A4088_A768-1864506.pdf

ceramic input/output caps: https://nl.mouser.com/datasheet/2/396/TaiyoYuden_UMR325AC7106MM-P_SS-1888209.pdf

Inductor: https://www.bourns.com/docs/Product-Datasheets/SRP1265A.pdf (10uH)

FET's: https://toshiba.semicon-storage.com/info/docget.jsp?did=54662&prodName=TPN11006PL