Hi,

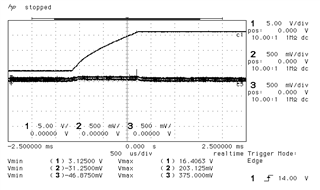

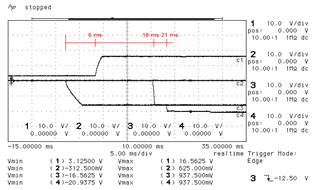

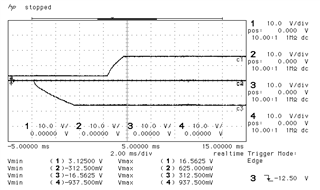

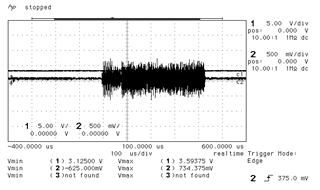

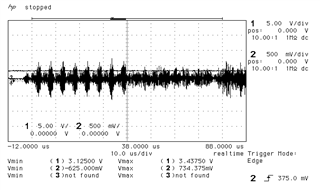

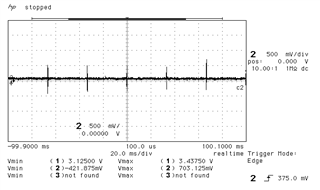

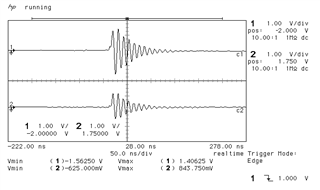

I'm trying to use a TPS65185 to provide power to an E Ink display. I've designed a board and assembled it, and while 5 out of the 6 voltage rails come up correctly, VDDH seems to fail to start. The PG register indicates that VDDH is not working (but the other 5 are). Probing VDDH with an oscilloscope, I see a "ringing" pattern centered around 0 volts:

Channel 1 (top) is VDDH, channel 2 (bottom) is VDDH_DRV. (note the location of the ground marker for each channel, on the left. Also note vmin and vmax for each channel, at the bottom)

This pattern repeats continuously until I shutdown the power rails by turning off the PWRUP pin. Is there a reason why this might be happening? I initially thought it could be that I was missing some capacitors, but I checked and my schematic seems to match the EVM and recommendations in the datasheet.

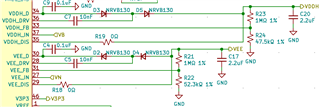

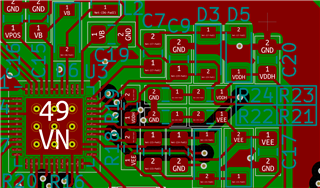

I assume there's probably an issue with my layout? Looking at it now, I can make some guesses as to what might be wrong:

- all the traces are the same width (0.2 mm = 7.9 mils) - some of the power traces should probably be wider?

- the board only has two layers, so the ground plane cannot fill everywhere and there's no +3V3 plane

- the capacitors and diodes for VDDH might be too far from the TPS65185?

However, I'm not really sure how those issues would cause this behavior. Any feedback and/or troubleshooting suggestions would be greatly appreciated!

The relevant parts of the schematic and layout are attached below (sorry they're a bit messy). I can also upload the rest of the schematic and/or layout if that would be helpful.

Thanks,

Alex