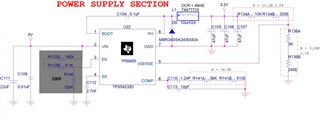

Other Parts Discussed in Thread: TPS54332

Dear All,

My design requirements is

Input : 5V and output : 3.3V, 1A

In my design I have used TPS54233 to generate O/P 3.3V,@1A. Is input voltage 5V sufficient for generating output 3.3V ? please find the attached schematic diagram and suggest.