Other Parts Discussed in Thread: BQ78350, , BQ76940, TIDA-00792

Hi,

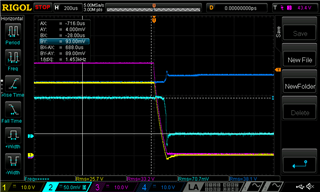

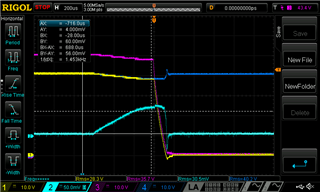

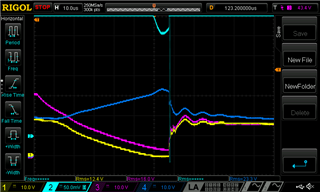

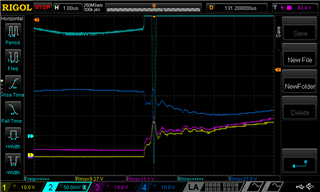

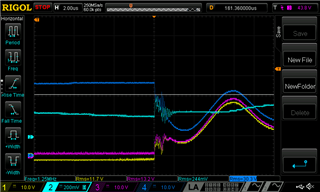

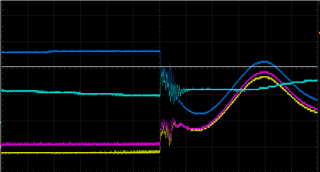

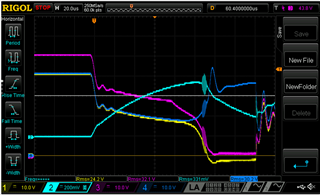

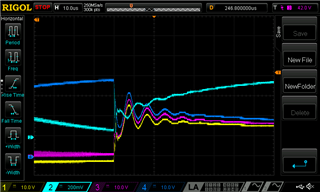

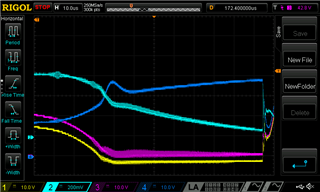

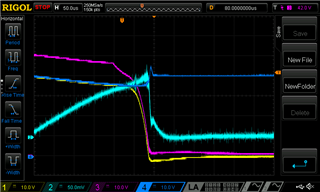

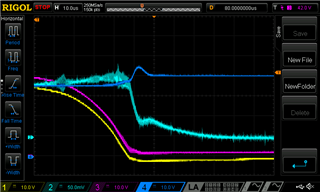

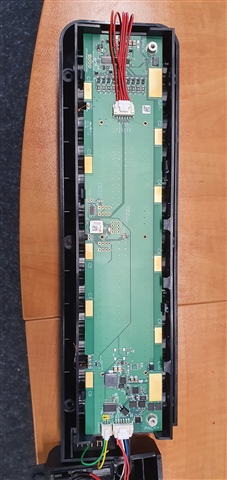

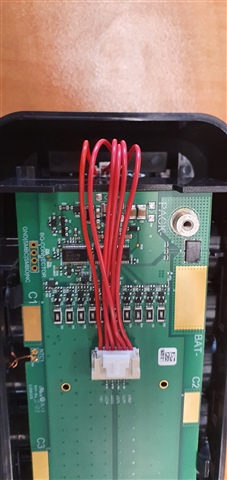

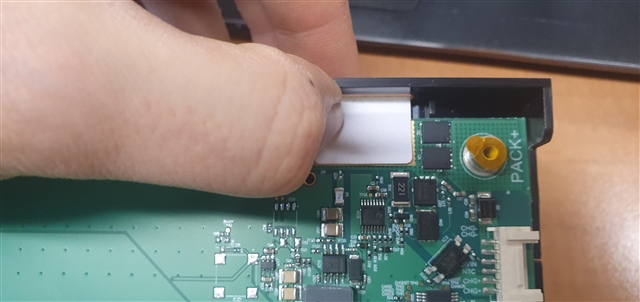

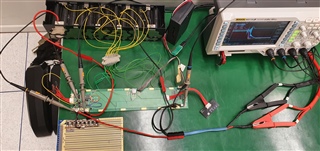

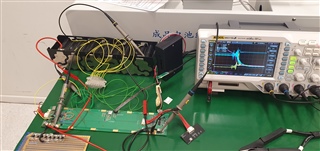

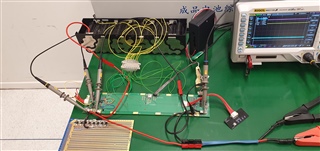

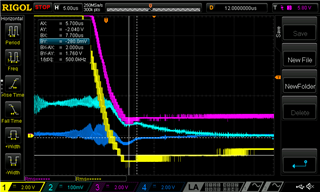

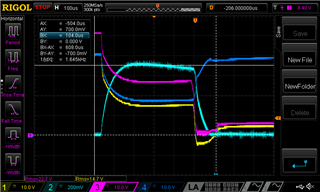

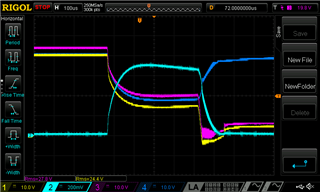

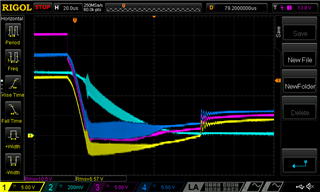

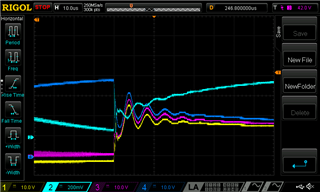

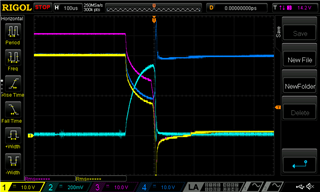

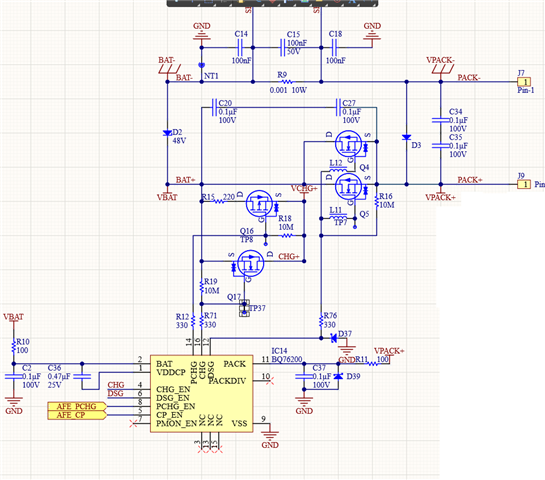

We are testing our design. During testing the hardware failed. One (of two) mosfets failed during a controlled short circuit test on the battery pack. Gate, source and drain are all shorted together.

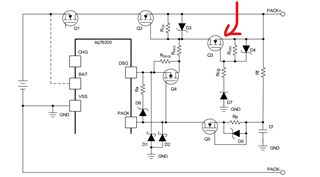

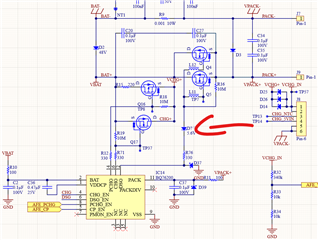

We use two NVMFS6H824NT1G in parallel (Q4 and Q5). After removing the broken mosfet (Q4), we can control the output again, so the BQ76200 doesn't seem to be damaged. We use the BQ76200 in combination with BQ76940 and BQ78350. This is the config file that we use: https://jasa8.dyndns.org/s/WtfRwn59DjbqS39

Probably the overcurrent killed the mosfet, but i think they should be capable to handle it for a couple of hunders of µs? Is our timeout to long or should we lower the treshold? Or is the issue related to something else?

Best regards,

Jan