Hi Team,

My customer is using this device & has a couple of questions regarding the reserved registers:

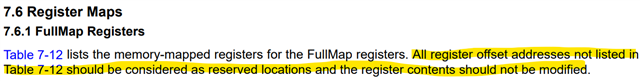

1) If registers not listed in table 7-12 are modified to different values, what will happen?

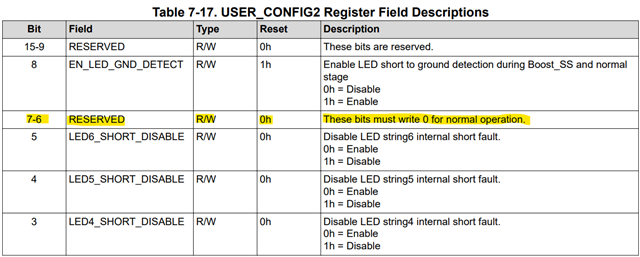

2) If Bit[7:6] of the USER_CONFIG2 register are modified to anything except 0h, what will happen?

Thanks for the support!

- Andy