Hi

For this application (a water turbine) I'm trying to convert the energy of of a 3 phase 48VAC PMSG to a stable 80V output with minimal ripple that can be delivered to an off the shelf solar grid-tied inverter (max input 600VDC). The 3 phase power is first rectified, passes some capacitors and is thant boosted by the lm5122 to the stable output. Input voltage can be between 20V and 65V DC, power range is up to 500W. I've got multiple questions from different nature, so if you think that I should split them up, please let me know.

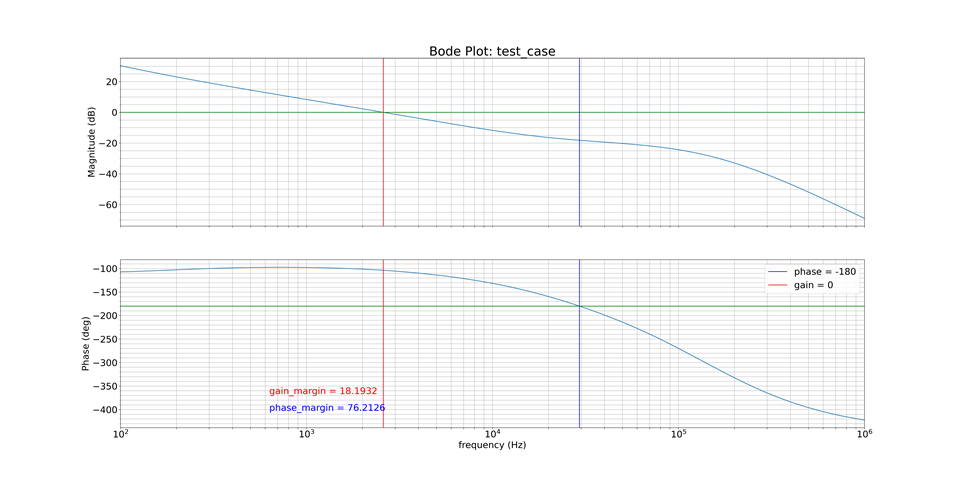

- I reconstructed the transferfunction which is given by the manual, but I got a different bode diagram. It looks like my frequency is about 2*pi larger than the one in the manual. Could it be that the frequency in the manual isn't the frequency in Hz, but in rad/s?

- The build up of the TF in the manual is a bit too condensed for me to tamper with it by myself so here are some modifications which I would like to simulate:

- At the output I have: 8 x 10uF ceramic capacitors and 8 x 100uF with an impedance of 0.17ohm @ 100kHz for each capacitor

- I currenctly added an additional LC filter, but I have no clue on how to add this in the transferfunction. The LC filter concists out of 4 x 4700uF capacitors with a tan(delta)=0.2 @ 120Hz and a torroidal inductor of 560uH. How do I add this Lc filter to the transferfunction? This wil for sure reduce my bandwith a lot, but the mayor ripple that need to be compensated is the ripple of the rectifier which is maximum ~70Hz, so I guess this isn't a big issue.

- Since I got a ripple in the input, which is high in amplitude, but low in frequency. Could it be an idea to feed forward this ripple to the COMP pin? I see there was a paper about this principlie: https://www.semanticscholar.org/paper/Feedforward-ripple-cancellation-for-a-full-bridge-Jackson-Leeb/2dd41c749d90e4a470947afcdb78d2d58b18152e . I already have a ripple extraction filter, but it isn't that reliable during low rpm's (the 50hz noise than get predominant), but we can solve this with the UVLO by not generating anything when the rpm (=voltage) is too low. May be this adds too much complexity?

- So for the 500W power this setup should be ok. As I look into a larger power range of generators I see that the output voltage of the PMSG inevitably goes up, so the LM5122. The next type of generator will be a 150VAC (203VDC), which is up to 1kW. Any ideas on which strategy / chip would best be followed than to convert this power? I guess control of the high switch will be a problem for the existing range of TI-products, so problably it will be a non synchronous converter?

- The solar inverter doesn't like it when the PCB with the Boost converter on is grounded to th earth. It generates an error in the inverter, which would make sense if this was about a damaged wire of a solar panels. So at first I disconnected the ground of the PCB from the earth. During operation I saw that my groundplane pretty fast went to a -200V difference with the earth. This didn't look safe to me, so in order to find a 'way in the middle' I connected a 1k ohm resistor in between the earth and the ground of the PCB. I didn't care about the wattage of the resistor since this floating voltage should only be low power. Now this resistor burned out quite fast. For now I let the ground plane floating: apart from connecting my computer by wire to the controller of the PCB and blowing 200V over my USB, to my grounded pc, does this involve any more risk?