Hi,

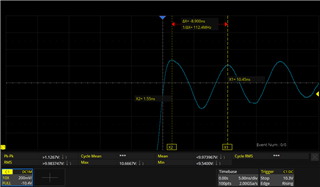

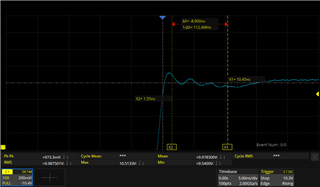

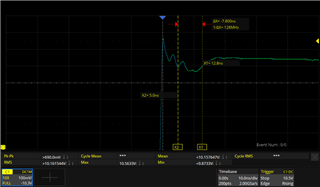

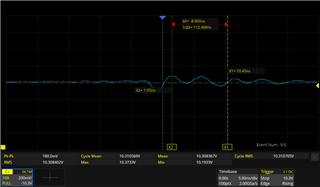

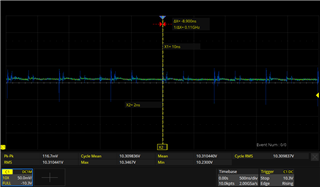

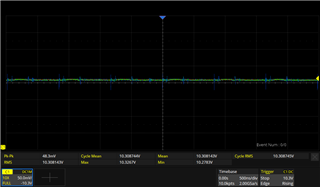

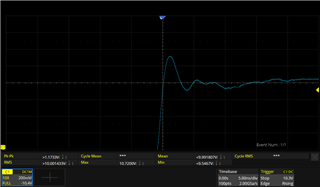

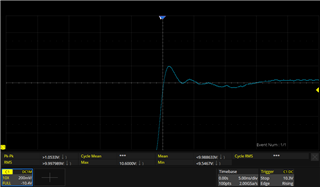

I have same problem as user6371168 (https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/937718/tps65150-tps65150) with noise on AVDD. Noise is bigger with no load. It's better without load, but still significant. After reading support by Liaqat Khan in this thread, I redesigned my PCB, but problem is still here.

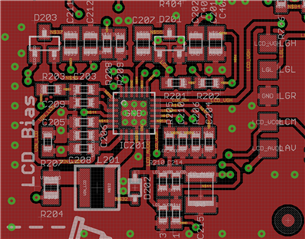

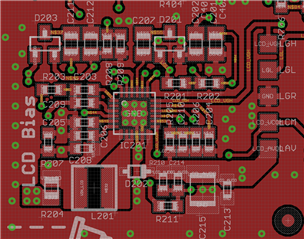

First PCB has only 2 layers of copper with one ground. 2nd redesign has 4 layer (1st signal + ground, 2nd ground, 3rd power, 4th signal + ground) and separated wiring of ground (power ground and analog ground) connected in one point with 0R resistor. Same issue on both board. So maybe is there problem with components...

Please see attachement for schematics and layouts.

I've tried two types of diodes (D202) on AVDD. 1st cheaper TS4148 RYG and 2nd more expensive, faster PMEG3010CEJ on both design of PCB, but with no effect.

Don't know where the problem is... Thanks for support.