Other Parts Discussed in Thread: UCC39002, UC3902, PMP6712

Hello,

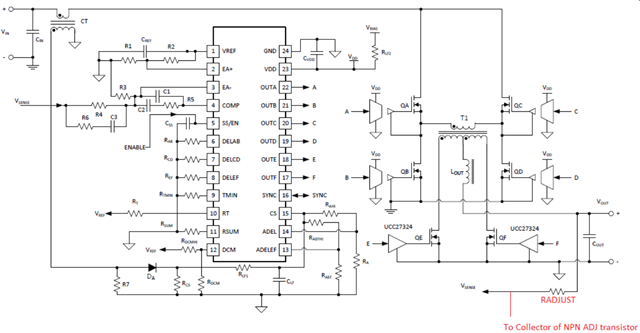

Consider a design similar to PMP6712.

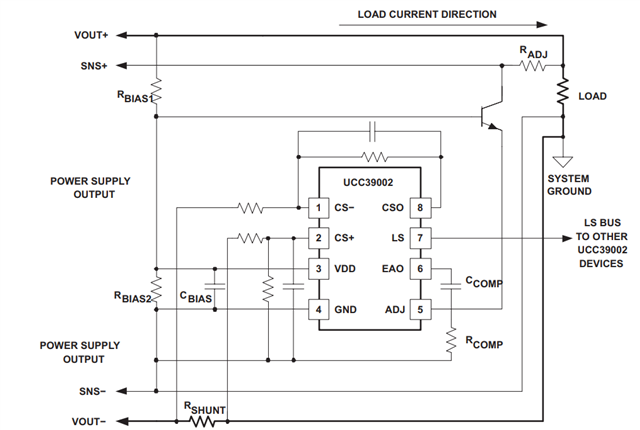

I'd like to better understand the factors that affect the current balancing between each power stage in a 2-stage design.

For instance, we have a number of units that have fairly equal and consistent current sharing, then once and awhile we get a unit that is skewed in one direction (i.e., stage 2 is always x-amps higher than stage 1).

Are there ways to correct/tune a unit to promote better current sharing?

Thank you in advance,

Iain