Good evening Rakesh, Good evening fellow forum users,

During testing with the TPS2492 I have come across an issue with the Overvoltage Protection of the chip and would like to ask you for advice, Rakesh.

For reference please find the schematic of the respective circuit below, which includes the design setpoints of the OV Protection.

8741.Schematic.pdf

When triggering the Overvoltage protection of the channel, the channel occasionally latches-off and will not turn on again when going below the limit (OV,falling), considering the hysteresis.

When trying to debug the issue I applied the following test sequence from a controllable voltage source

1) Start at Vin = 32V

2) Ramp Voltage to 36 V within 2s (trigger OV Protection)

3) Hold Voltage at 36 V for 2 s

4) Ramp Voltage down to 22V within 2s (go below OV,falling)

5) Keep voltage at 22V

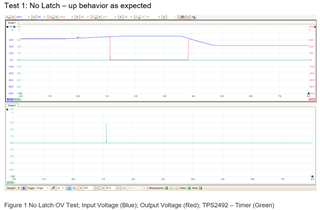

In figure 1 you can see the regular expected behavior of the circuit. The Gate driver shuts down the channel when surpassing 35.4 V and turns it back on when falling below 33.1 V

In some cases for the same sequence the following (figure 2) happens: The Gate driver shuts down the channel, but does not restart when falling below OV,falling.

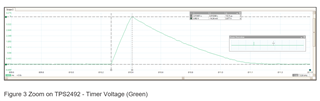

I measured the voltage on Ct for the latching case and surprisingly it hits 4V while going below OV,falling. As a consequence the channel latches off.

When zooming in on V(Ct) it is recognizable that Ct is getting charged with roughly the 27 uA you would expect during power limit/current limit event according to datasheet:

Datasheet P.8: The timer charges at 27 µA whenever the TPS2492/3 is in power limit or current limit and discharges at 2.7 µA otherwise

To exlude that the gate driver is actually switching at this point of time, I scoped the gate-source voltage of the Mosfet, but no turn on event of the Gate driver can be observed:

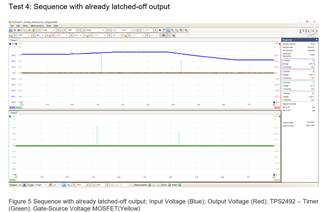

Now out of curiosity I tested the same sequence on an already latched-off channel and the following was the result:

Even for a latched-off channel there is some significant rise in V(Ct) when the OV surpasses OV,rising and falls below OV,falling.

What causes this rise on V(Ct) and the consequential latch-off and how can we fix this problem?

In our application the latch-off is definitly not intended.

I appreciate your help. Please do let me know, if I can provide any additional info or do additional tests on the way to a solution.

Cheers

Konstantin E.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.