Hello,

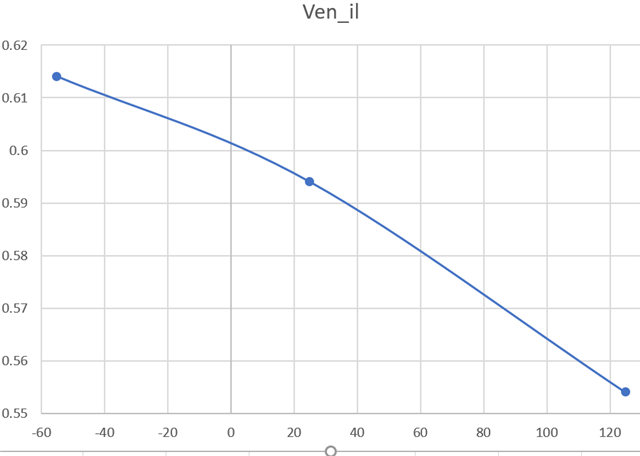

While performing WCA, I've noticed that VENILmax is quite low at 0.3V over full temperature. I assume that VENILmax could be increased if not used over the full temperature range. My application junction temperature is only 80C or 90C. Could I please get a VENILmax per my application junction temperature?

Thank you.