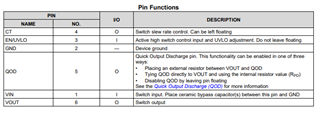

The data sheet of the TPS22810-Q1 contains a table with different values for the CT cap.

In the table there are also rise times for CT = 0 F

Also at different positions in the data sheet there is either the CT completely ommited (e.g. Fig 19 and 20) or specified as CT = 0 F (e.g. Fig. 28 and 31).

However, in section 8.3.4 Adjustable Rise Time (CT), the CT capacitor is not specified as optional part of the circuit (such as for the Cin and CL).

I have 3 TPS22810-Q1 in my design

#1: Vin 3 to 18 V, Cin= 22uF, CL= 0 F, CT= 0F

#2: Vin 5.3 V, Cin= 1 uF with uF, CL= 0 F, CT= 0F

#3: Vin 3.3 V, Cin= 1 uF with uF, CL= 0.1 uF, CT= 0F

So just to be sure,

Q1: I assume the TPS22810-Q1 can function properly with CT pin not connected and floating as implemented in my current design? Or is using a CT mandatory...?

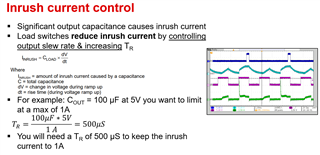

Q2: In Fig. 28 and 31 of the data sheet the inrush current is shown for CL = 22 uF and for 100 uF with CT = 0F. I am wondering what is limiting the inrush current in these cases to around 1.8 A and 7.5 A respectively?

Thank you,

Michael