Hi,

we are using TPS650930 for our Intel Xeon E-2254ML processor board.

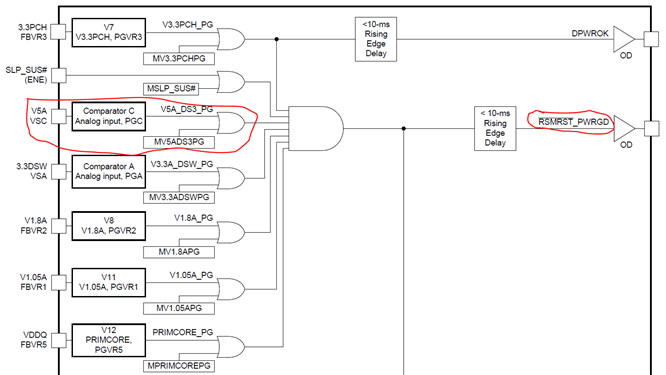

At the TPS650930 comparator section, we have connected Comparator-C(VSC & ENC) to ground as we are not using comparator-C.

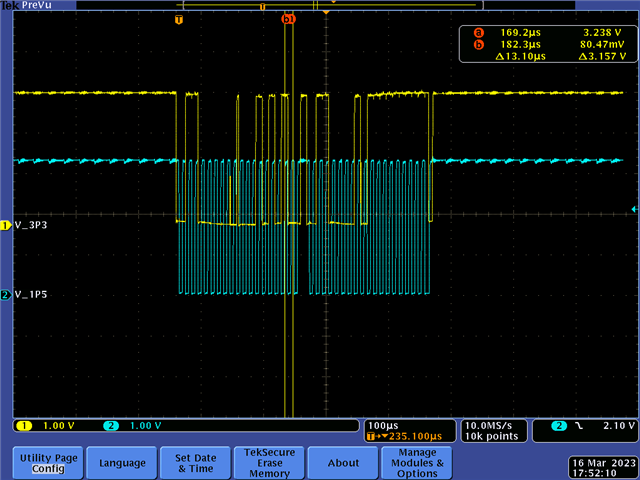

once the board is powered on, we have observed that RSMRST_PWRGD# output from PMIC is always low due to which my PCH is not generating sleep signals.

please help us to solve this problem.

Note:- Except Comparator-C all other comparators voltages are properly given and working as expected.

Attaching the Schematics of comparator circuit.

Thanks and regards,

Ravi babu