Hi Team,

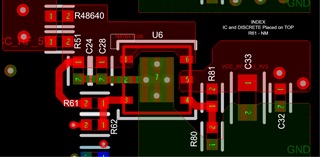

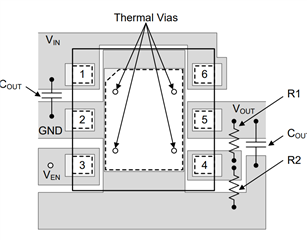

We are using the LP38692SD-ADJ/NOPB LDO part in our Layout Board file. I had attached the images of the Board file and Schematics. Please review the layout and share your feedback with us.

The PCB we are using is of 12 Layers:

IC - Place on top

Layers 2,4,9 and 11 are Ground

Enable Signal is from L5

Thanks and regards

- Teja.