Dear Sir/Madam, hi.

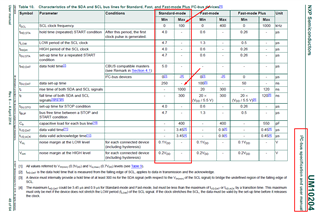

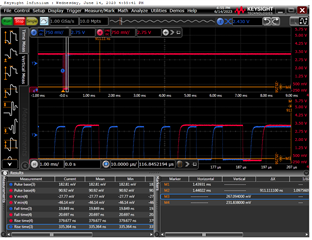

According to the LP5562 specification [1], the maximum SCL/SDA rise-time requirement is 300nS (Table 6.8, page 6), the same as described by the I2C standard [3] (Table 10, page 48) for a Fast-Mode (400kHz clock). But I'm using the Standard mode up to 100kHz (in my case 90kHz), and the standard [3] requirement for the Standard-Mode (100KHz clock) is 1000nS. Does the 300nS requirement still stand for the Standard-Mode (100kHz clock)? Or the rise-time requirement for the Standard-Mode is described at the standard [3].

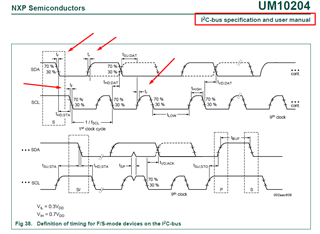

Please note I'm measuring the rise-time as described in a previous thread [2], 10% to 90%, which differs from the standard [3] described in Fig-38, page 50.

[1] https://www.ti.com/product/LP5562

[2] https://e2e.ti.com/support/power-management-group/power-management/f/power-management-forum/1021633/lp5562-rise-time-and-fall-time-of-i2c

[3] https://www.nxp.com/docs/en/user-guide/UM10204.pdf

[4]