Other Parts Discussed in Thread: UCC28950,

Hello,

My system consists of 3 modules paralleled at 24V and each doing 1100W, for a total load of 3300W. Each module has a UCC28950 and a load share UCC29002D.

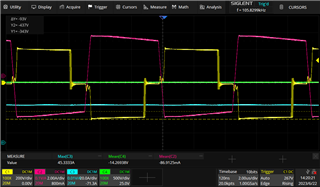

When I run each module independently at full load, I get pretty stable waveforms as seen below in Figure 1.

Figure 1: Pink Shim inductor current and Yellow H-bridge on Module 1 (running by itself).

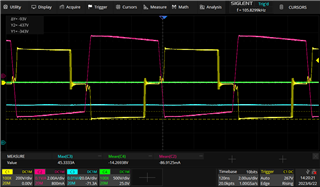

When I run two modules together at full load, my H-bridge and Shim inductor current appear to be pretty unstable like shown below in Figure 2 on both converters. The same occurs when I run 3 modules together.

It is worth noting that each module IS successfully current sharing, it is just the instability that is causing on my system that needs to be solved.

Figure 2: Pink Shim inductor current and Yellow H-bridge on Module 1 (when 2 modules running together).

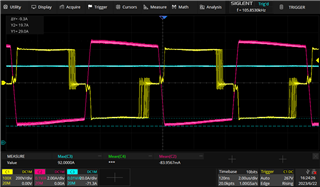

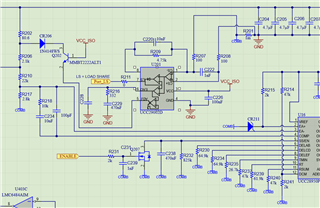

This is the circuitry regarding the UCC29002D that I have on each module:

Please let me know if the Load Share has been setup correctly or if there is anything that I can do to solve this problem.

Thank you,

Alberto Miguez