Hello Team,

Customer is in the process of designing with the TPS51362.

Regarding TPS51362, customer has conducted some tests as outlined below.

Could you please help clarify the impact of LP# on the Converter?

Vin = 20V, Vout = 1.8V

- LP# = always LOW, customer see no issues under both light and heavy loads, the output voltage maintains at 1.8V.

- During load pull, if LP# is pulled LOW, it doesn't affect the output voltage (maintains at 1.8V).

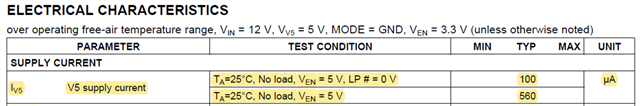

- With LP# = LOW and no load, IV5 measures 0.035mV/100mΩ which equals 350uA.

- With LP# = 5V and no load, IV5 measures 0.075mV/100mΩ which equals 750uA.

- Whether LP# = LOW or floating (5V), the output remains unaffected under both steady and transient loads.

Thanks for your assistance.

Best regards,

Scott