We do the dynamic load from 0A to 120A, step load 2A/us, 3kHz frequency 90% on /10% off, during the AC On/Off with dynamic load. We find the loading start from the VDD low than 3V, than the Vgs is going unstable. It has a negative gate voltage charge and discharge frequency. When we start the loading from the VDD high than 3V, then the gate voltage can work normal.

May I learn from you about what the reason cause the gate voltage become negative and charge/discharge frequency? I had tried to increase the BYP cap to 0.01uF, and VDD cap to 2.2uF, but all are not have any improve.

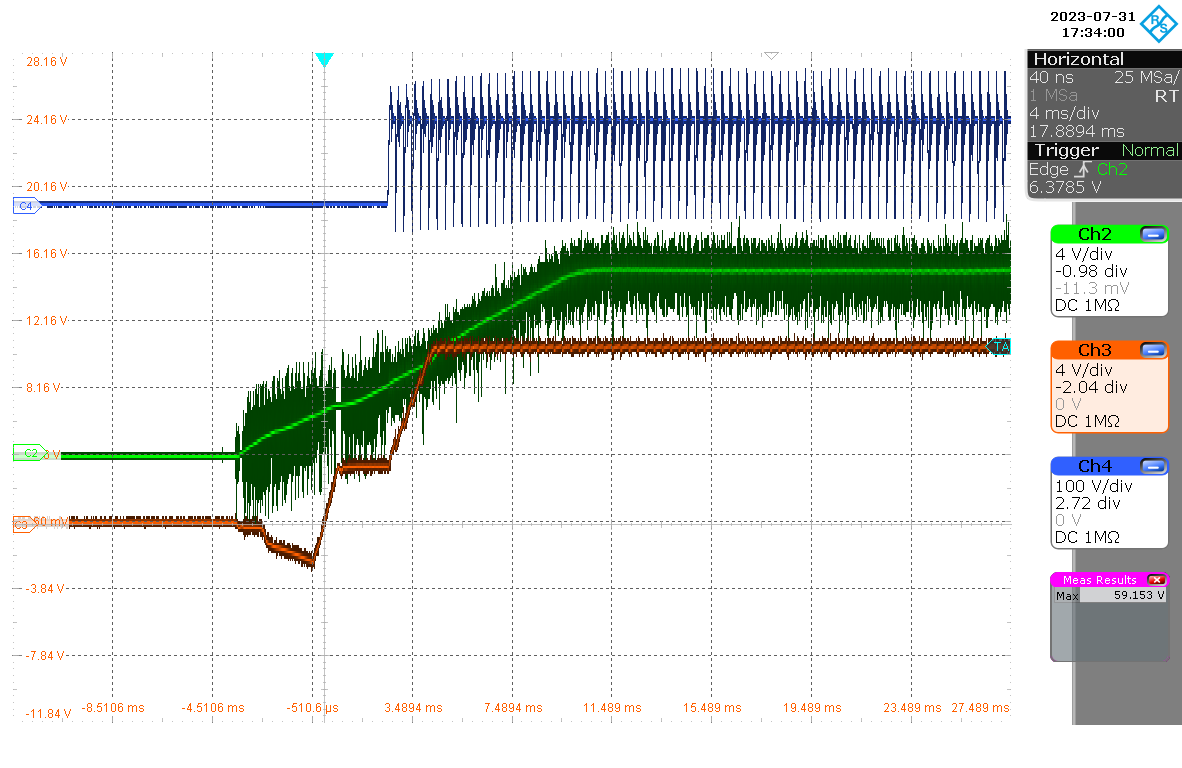

C4(Blue): Output current, C2(Green): VDD_TPS2412, C3(Orange): Vgs_OringFET

The loading start from the VDD low than 3V.

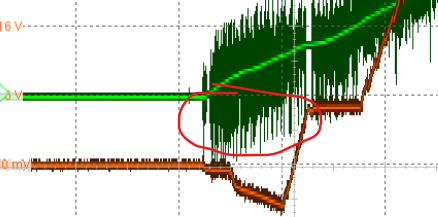

C4(Blue): Output current, C2(Green): VDD_TPS2412, C3(Orange): Vgs_OringFET

The loading start from the VDD low than 3V.

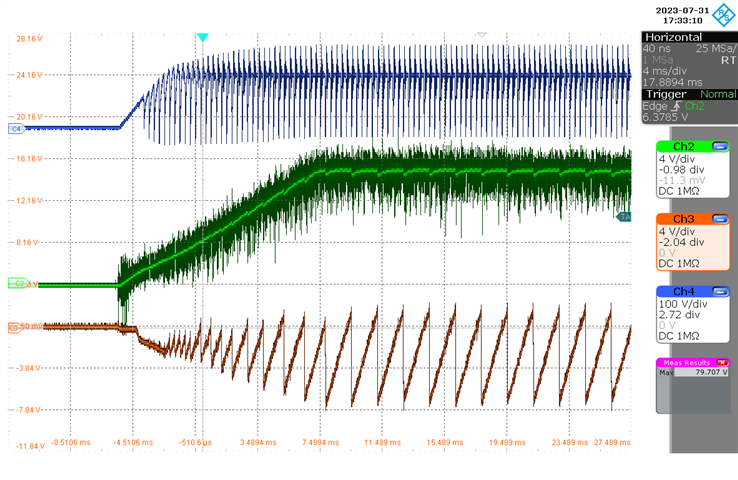

The loading start from the VDD high than 3V.