Good morning,

I contact you because i can't simulate my TPS62872QWRXSRQ1 application.

In fact, the webench doesn't simulate this part and that is a problem for me. In the Design tools & simulation, there is the AVG simulation on Pspice and the transient on Simplis.

However, my company can't afford the license of Simplis and the simulation is too complex for the demo version.

So, today, i can only simulate bode diagram. Is it because this component is too recent ?

Is it possible to have the Pspice model of the TPS62872-Q1 transient analysis?

Or is there any other way to simulate the transient ?

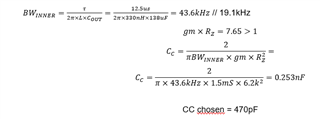

Please find below my design :

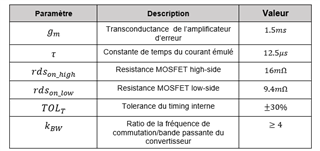

Here are my parameters :

VIN = 5V

VOUT = 0.85V

IOUT = 6A

F_sw = 2.25MHz

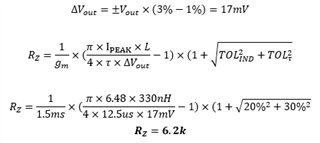

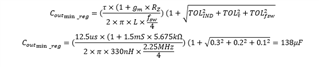

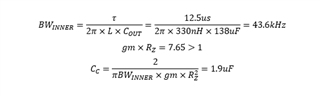

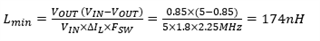

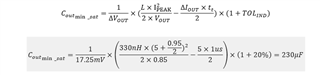

Below are the values calculated :

Self : L = 330nH

Output capacitor : Cout = 300uF

Compensation network : Rz = 5.1kOhm // CC = 2.2uF

Input capacitor : Cin = 122uF (for energy storage)

Thanks for your support,

Best regards,

NEANNE Florent