Hello,

I'm trying to get theTPS38700 running but so far we're finding that the sequence outputs just remain low and also the /RST output stays low. We had something that worked with the dev board so wondering if there's anything obvious that's wrong.

I know the dev board uses the automotive -Q1 part while the part we have on the board has the consumer part (TPS38700C04NRGER, i.e. not the -Q1 part). From a check of the datasheets, the only difference seems to be that PEC is initialised to 0x00 in the -Q1 part and initialised to 0xFF in the consumer part. Is there any other change in register programming that is required?

I also note from datasheets that the voltage range for a high input on /SLEEP and ACT signals only goes up to VDD-0.2V. At the moment the signals are direct from a MCU on the same supply so these signals will be very close to VDD. If they are at VDD, would the TPS38700 not recognise this as a high level, and therefore prevent the sequencing from starting when both are driven high?

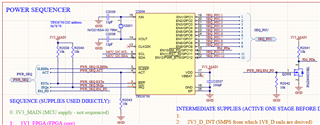

Fragment of schematic below, if it helps.

Thanks,

Gordon.