- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

We already exchanged on one of our design on the linked post with yihe.

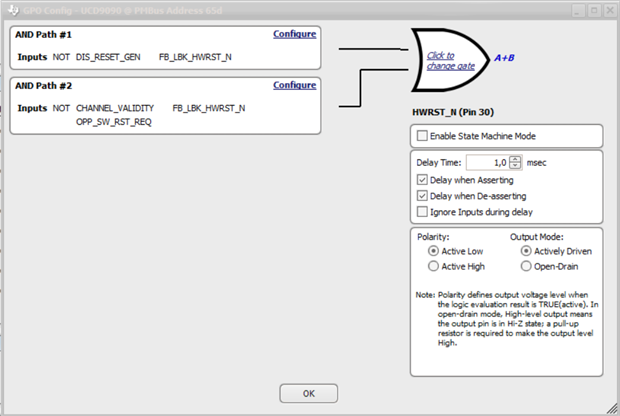

We are encountering a very strange issue with that same design, on the equation of the TMS_GPIO21 output pin (HWRST_Ni on the schematic sent through our FAE Franziskus Hillreiner).

The configuration of the GPIO is the following :

All signals except the FB_LBK_HWRST_N are active high inputs.

We have checked on the board with an oscilloscope and all the inputs except the FB_LBK_HWRST_N are low. However, we would have expected HWRST_Ni to be high at board level and it is low.

We confirmed these levels with the Monitor task in Fusion Digital Power Designer.

This does not make sense.

We encounter this behavior after some tests which leads to the FB_LBK_HWRST_N toggling (due to UV generated on the MON inputs) between high and low with DIS_RESET_GEN low to ensure the HWRST_Ni is not set during these tests, when we set DIS_RESET_GEN back to high state after FB_LBK_HWRST_N being high during at least 40ms.

We do not encounter this behavior each time, we couldn't figure out a pattern of occurence, and it happens on two UCD9090-Q1 of our board.

Anything you see we could be doing wrong ?

Best regards,

Clément

Yihe,

I think you already have the project file, it was sent to you by Franziskus along with the schematic in Juy.

Do you still have it ?

Best regards,

Clément

Hi

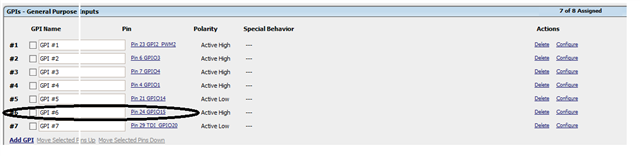

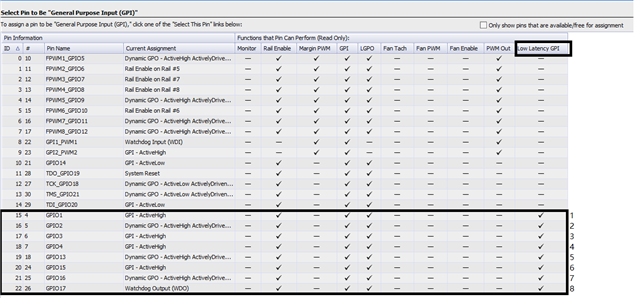

The issue is that Pin24 GPIO15 can not be configured as the 6th GPI. You have to swap it.

The general rule for those low latency GPIs, those GPIs can not be assigned to based on the number(1-8) listed below.

For example: GPIO1 can not be configured the1st GPI. GPIO17 can not be configured as the 8th GPI

Regards

Yihe

Yihe,

Where is that information stated in the documentation ?

Does it mean that the GPIO state change isn't taken into account because it's low latency ?

Also, we only have #7 GPI, so we can't swap it so that it goes above 1-8, will that work ?

Clément

Hi

When the GPI is configured as low latency GPI, the state of the GPI may misbehave.

what you need to do is to not configure GPIO15 as the 6th GPI. you can configure 1st, 2nd. 7th. but not the 6th.

Regards

Yihe

Hi,

Ohhhhhhhh, gotcha. We will try.

I would suggest that you implement a warning in the software then if that's the case.

Best regards,

Clément

Yihe,

We switched #6 with #7, made the sure the equations were good after the change and the behavior is now even more erratic.

The state of the GPIO15 just does not seem to have any impact anymore on the output result of the GPO #5 equation...

Best regards,

Clément

Hi

That's impossible.

You may need double check LGPO setting and also you have to power cycle the board to let the new settings take effect.

Please send your new files.

please ensure that the file hast the proper name. the previous file does not have name and it is hard to follow

Regards

Yihe

Yihe,

What do you mean by double LGPO setting ?

I'll get back to you on Friday.

Clément

Hi

I mean double check your LGPO setting to ensure that the right GPI is set.

Regards

Yihe

Hi,

The issue was a side effect from another function following the working change.

So your suggestion did solve our problem.

One question remains, where is that constraint/issue documented in your technical documentation ?

Clément

Hi

Thank you for the feedback. will will take action for the future releases.

Regards

Yihe