Other Parts Discussed in Thread: TINA-TI

Dear experts,

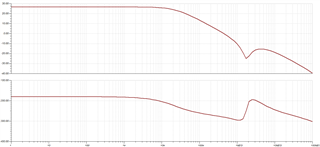

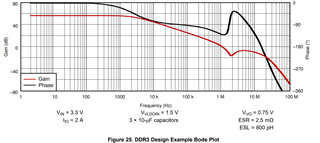

I simulated bode plot of DDR3 design with TINA-TI Average Spice Model (SLUM151), I set the conditions the same as those described in Figure 25(DDR3 Design Example Bode Plot )in data sheet. However, there was a great difference between the bode plot shown in data sheet and simulation result.

Could you please elaborate on this difference?

Best Regards,