I am facing UV problem for LP8764-Q1 on system reliability qualification. The fault report as following:

mfg-s32g> i2ctransfer -f -y 1 w1@0x20 0x5a r1

0x91

mfg-s32g> i2ctransfer -f -y 1 w1@0x20 0x5b r1

0x02

mfg-s32g> i2ctransfer -f -y 1 w1@0x20 0x5d r1

0x02

mfg-s32g> i2ctransfer -f -y 1 w1@0x20 0x66 r1

0x01

mfg-s32g> i2ctransfer -f -y 1 w1@0x20 0x69 r1

0x02

------------------------------------------------------------------------------------------

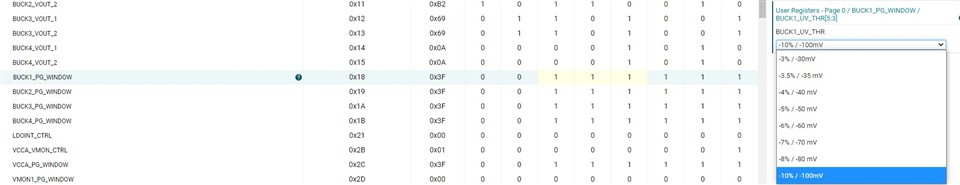

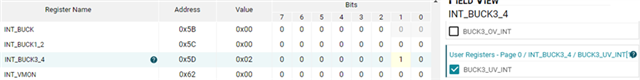

The log indicates the fault is caused by Buck3 interrupt with UV event.

mfg-s32g> i2ctransfer -f -y 1 w1@0x20 0x5d r1

0x02

Currently, I suspect this should be an OCP event causing Vout drop. Some of question should be clarified below.

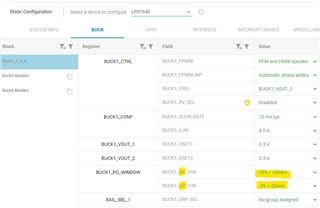

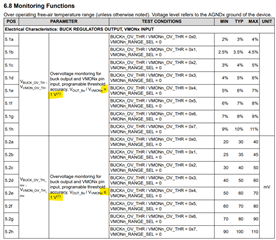

- How is the definition of UV trigger level? Is this Vout*90%?

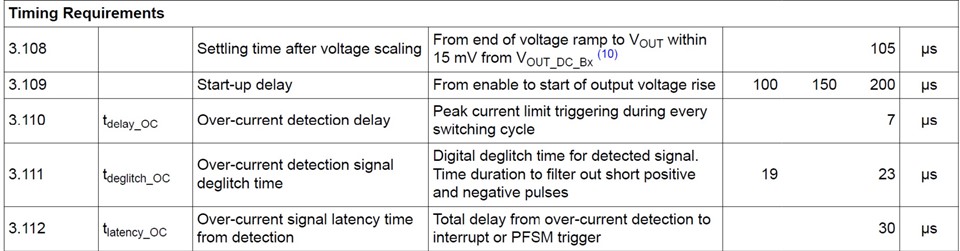

- OCP fault will be reported if the load current above the limit level for 30us, right? If we do not see this fault, the Vdrop might result from high transeint load or other reason?

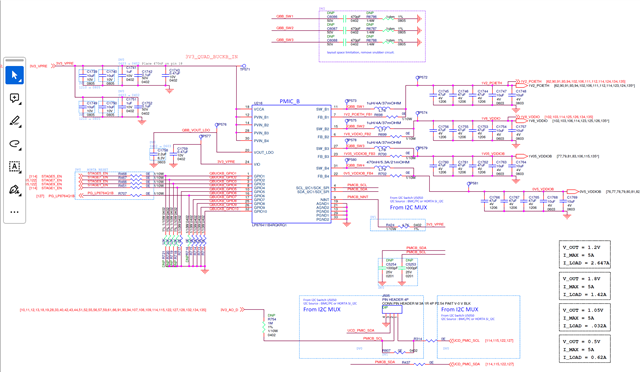

BTW,here is current schematic. Please ignore the Iload information.