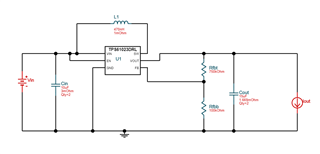

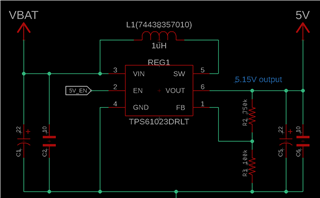

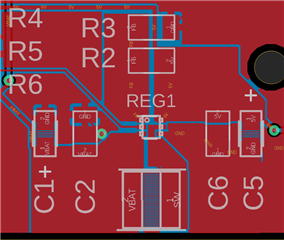

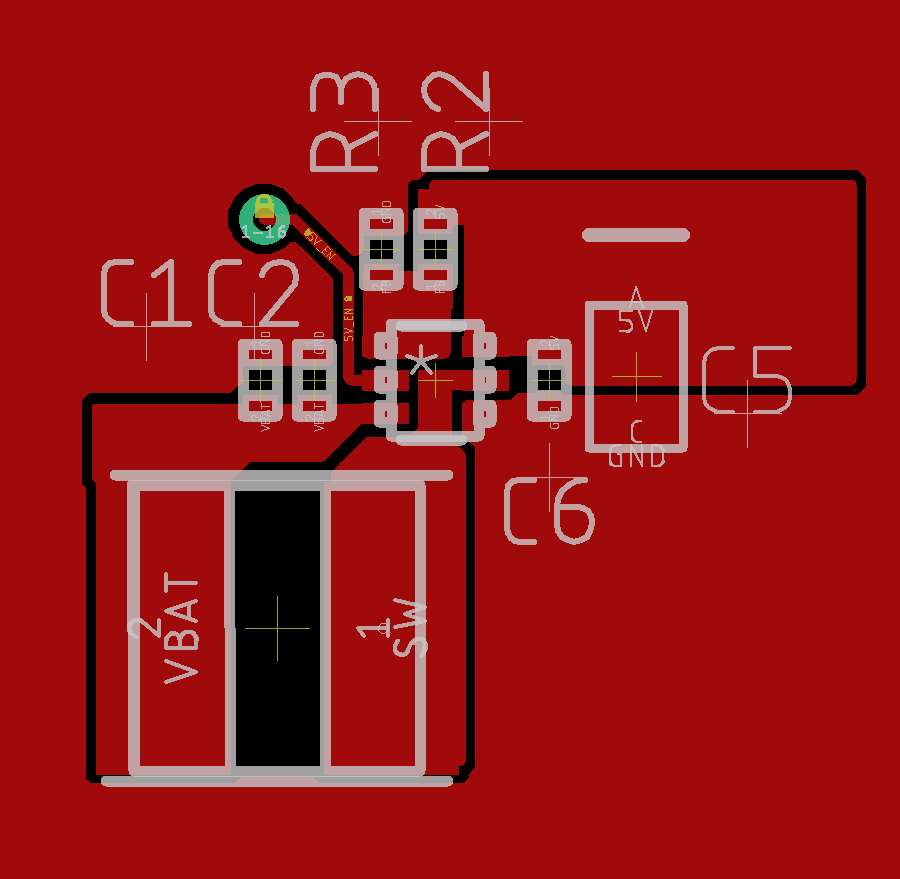

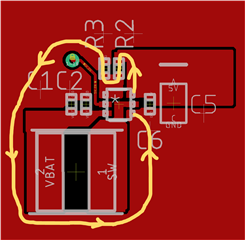

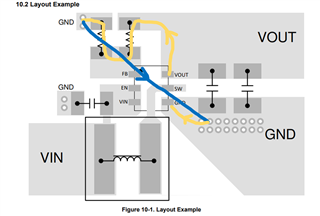

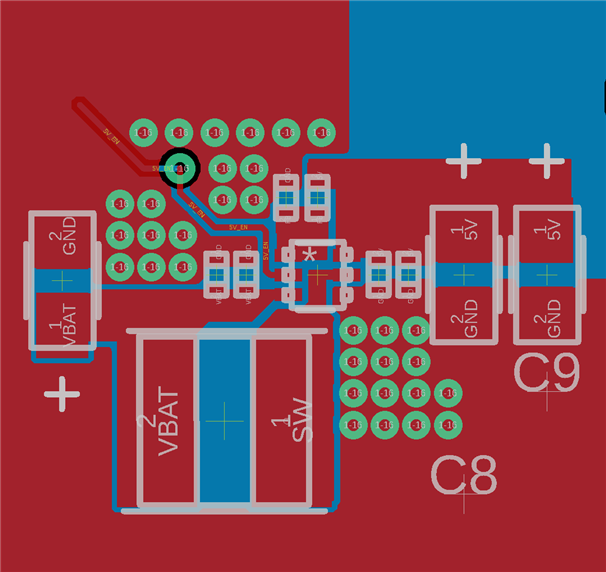

So I built this circuit using webench. I've attached the SCH & PCB. It's a simply 2 layer PCB, not much going on.

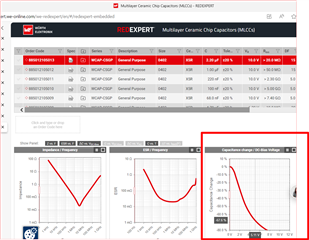

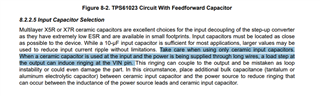

The circuit outputs 2.15V as advertised. Currently I have a 200mA load connected, everything is hunkey dorey. When I bring my finger close to the chip itself, the voltage begins to increase. The closer my finger, the higher the output voltage until my finger touches the chip and it fries and creates a dead short from VIN to GND. I've done this twice! On the third time, I added the feed forward capacitor (as recommended on webench) of 1pF as a "what else to do" solution. My logic was stray capacitance from my finger was influencing the FB pin somehow (hence the increasing output voltage). The same thing happened. What on earth is going on here? What do I even try to start troubleshooting?