Other Parts Discussed in Thread: TPS3823, TPS3828, , TPS3824

Hi,

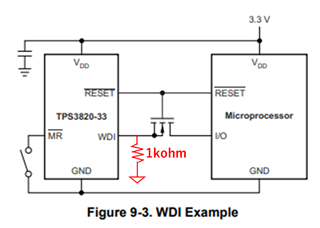

The datasheet page 15, 8.3.4 Watchdog Timer (WDI) contains the following information:

”The watchdog timer can be disabled by disconnecting the WDI pin from the system. If the WDI pin detects that it is in a high-impedance state, the TPS3820, TPS3823, TPS3824, or TPS3828 will generate its own WDI pulse to ensure that RESET does not assert.”

I have any question.

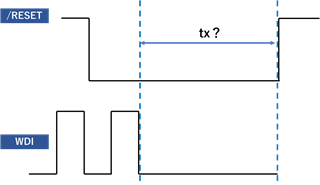

1) Is it correct to understand that if a WDI transition is entered even once when /RESET=Low, /RESET is fixed to Low?

2) If a WDI transition is entered and /RESET=Low, is there a way to be /RESET to High?

3) Is it possible to be /RESET to High by controlling /MR or by entering a WDI transition again?

Best Regards,

Nishie