Other Parts Discussed in Thread: CSD19532Q5B

Hello,

We are considering LM5118 for an application with the following requirements

Vin (min) = 18V

Vin (max) = 75V

Max load current = 3A

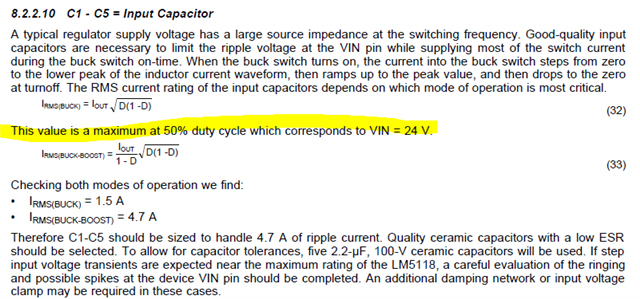

In the datasheet, I came across information suggesting that the RMS current rating is at its maximum at a 50% duty cycle, corresponding to VIN = 24 V. I would like to seek clarification and additional details on this matter to better understand the product's behavior in our application.

Additionally, if there are any specific considerations or guidelines for optimizing performance under varying duty cycles, I would greatly appreciate your guidance.

thanks

Najma