Other Parts Discussed in Thread: TPS1H000-Q1, TPS7B7701-Q1

I'm looking for a 12V 150mA fold-back current limiting IC with low-dropout (12V input and 12V output) for a high reliability and high efficient power supply project.

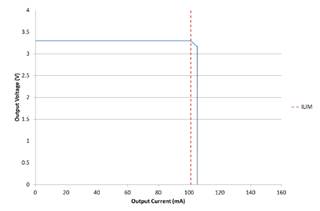

I tried some Single-Channel Smart High-Side Switches, but they didn't meet my needs because they only offer constant current or hic up limiting modes with an ON time longer than 1msec. I'm looking for a Fold-back IC or smart switch that can limit the current to 150mA in a fold-back manner or a hic up Smart Switch that has an ON time shorter than 1msec.

Do you have any suggestions or recommendations for such a device?

Kind regards