- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

hi

To inquire about Pmic fault development, I summarized the following questions according to the description of TPS650332-Q1 data manual and my own understanding. Could you help me answer them?

Problem 1: The values read are not consistent with the manual, and it is not possible to determine whether the data we read is correct.

Question 2: The write to the Pmic register cannot be written at present. Are there any corresponding rules or certain conditions for the write operation?

Question 3: For the development of Pmic faults, the reading register corresponding to the fault status bit is used as the basis for judgment. Is there a corresponding fault injection condition that causes the change of fault status? No corresponding fault injection method is currently found in the safetymanual documentation.

Hi there,

The OPN "TPS65033200-Q1" has I2C_CRC enabled; all registers operations need to have the CRC byte inserted as described in its datasheet.

Please check this FAQ for "How to make CRC for TPS650332-Q1 I2C communication".

Thanks!

Phil

At present, the value of the chip register 0h (PID) is 0xda, and the value of the register 1h (RID) is 0x59 by the IIC tool or program.

The Reset values indicated in the manual (tps650332-q1 datasheet) are (PID) 0xd0 and (RID) 0x09 respectively.

But write can't write data.

The read value is inconsistent with the manual. We need to confirm whether the data we read is correct.

Hi Thundersoft,

From what your I2C reading, the device OPN should be "TPS6503320A-Q1" with NVM revision 5.

TPS650332-q1 datasheet provides register values based on OPN "TPS65033200-Q1" which has (PID) 0xd0 and (RID) 0x09 respectively.

Thanks!

Phil

Hi Phil,

Thank you very much for your answer.

Based on your conclusions, we can confirm that the values we read are correct.

There are still a few questions that need to be answered.

Problem 1: However, the current write to the Pmic register cannot be written at this time.

Are there any corresponding rules or certain external conditions for the chip write operation?

Problem 2: For Pmic fault detection, the fault status bit of the register is read as the judgment basis.

Are there appropriate fault injection conditions that can cause changes in register fault status bits?

There is currently no corresponding fault injection method in the security manual documentation.

Hope to provide a solution.

hi

Thank you very much for your answer.

I would like to ask I2C communication to insert CRC bytes, can this operation give an example of assigning a value to a register?

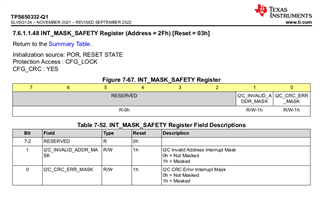

For example, in the figure above, register write operation, how to enter parameters, how to insert CRC, whether there is a register configuration can unlock the register write.

Is there a detailed list of relevant registers?

Hi, Phil.

It seems that this reference descripes a methods using HW. Is there a SW methods to reject the fault?

For example: Using a script to write the fault value to the fault register, and the status register will auto-change to fault status according with the fault register. SW will check the status register to confirm if there is the fault.

Thanks.

Hi Yuting,

I actually read it as "inject"; so, same answer to your question.

Thanks!

Phil