Hello,

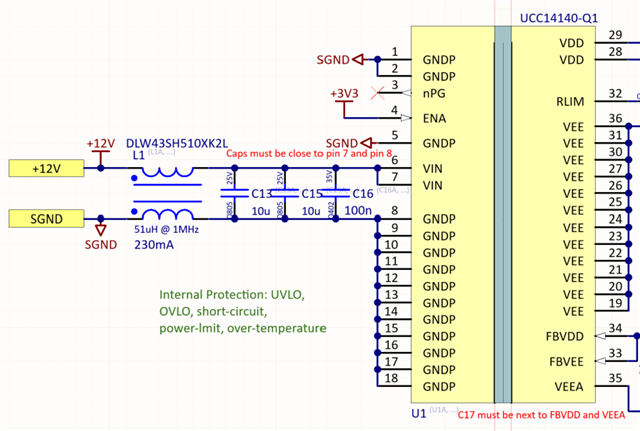

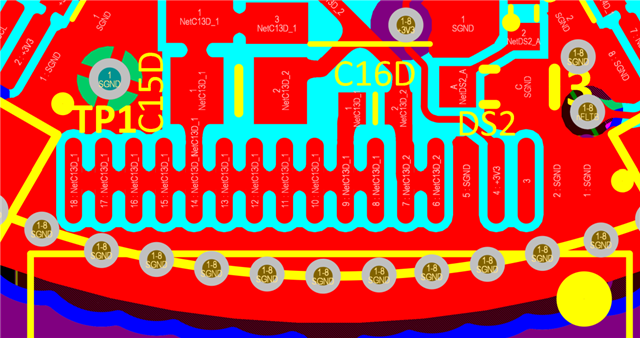

We're working on updating our gate driver design for our three-phase two-level SiC inverter to utilize the UCC14140-Q1 and I had a question about paralleling the inputs and common-mode provisions. We previously used a common-mode choke on the 12V input to damp any common-mode currents that traveled across the isolation capacitance in the high-side PSU due to high dv/dt (10-20V/ns) on the switch node. See image below.

However, when using the UCC14140-Q1, this creates a problem. This means we cannot connected the GNDP pins to the SGND plane for heatsinking.

What is the recommended solution here? Is the common-mode choke unnecessary? I don't see any recommendations in the datasheet for it.

One thought we had was to have LC filters on the GD PSU inputs to to avoid diff noise coupling between the PSUs and then have a single common-mode choke on the 12V input to prevent CM current from getting into switching converter that is producing the 12V role. This would allow us to tie the GNDP pins to the SGND planes for heatsinking, but CM current could still aggress from one PSU to another. Is this an issue?

Thanks,

Jason