The output of the push-pull converter is used as the bus voltage to supply the single-phase inverter H-bridge (i.e. realizing the conversion of DC24V to AV380V, 50HZ)。The inverter output adopts an open-loop method

The output voltage of the single-phase inverter is AC380V. The four MOS transistors powered by the single-phase inverter H-bridge are driven by the PWM of TIM1 in the AT32F415 microcontroller. The H-bridge circuit diagram does not provide it. The current problem is:

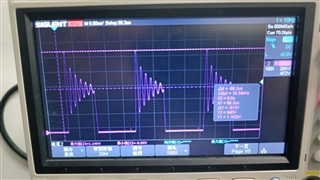

When inductance L3 is present, when the inverter output carries a load of 500W, the peak voltage of MUR8100 may sometimes exceed 1KV, causing MUR8100 to explode. What is the cause of this voltage peak? How to eliminate voltage spikes?

When the inductance L3 is removed from the push-pull full bridge rectifier output, the MUR8100 bears a peak voltage of about 600V when the inverter output is loaded

May I ask why inductance causes an increase in peak voltage?

Thank you!

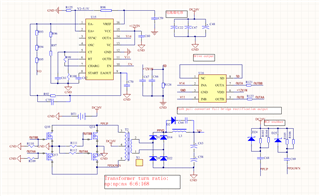

Input: DC 24V (Two 12V7AH battery)

Output: DC 550V

Full bridge field-effect transistor: MUR8100

Transformer turn ratio: Np:Np: Ns (6:6:168)

PWM frequency: 30KHZ

Inductance(L3): 10mH

Capacitance(C58,C63): 68UF/400V

The principle diagram of the push-pull converter for full bridge rectification is as follows figure1

figure1