Hello team,

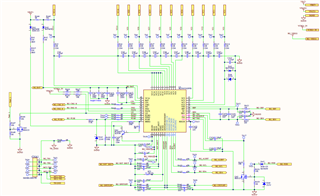

We are currently utilizing the bq76952 in our product, and we've encountered an unexpected issue during our testing phase.

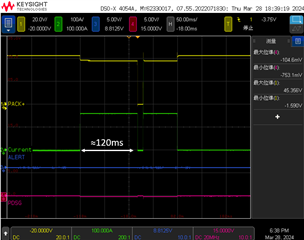

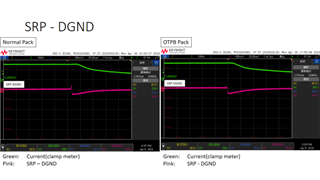

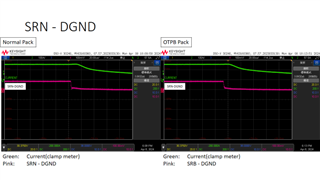

While testing the OCD1 protection feature, we observed some unexpected behavior. Specifically, when the current reached approximately 263A, the value of the [0x12] Battery Status Register transitioned from 0x0180 to 0x0100. This indicates that the OTPB bit was reset. Concurrently, the cell voltage reading became incomplete, with registers 0x1C through 0x26 displaying zero values. Additionally, the temperature reading reset to 273.15.

However, upon turning off the Eload and reducing the current from 263A to 1.2A, the system appeared to function correctly again.

The setting of the OCD1 : { threshold = 152A, delay = 118.8ms }

We have verified the accuracy of our logs using a logic analyzer to parse the I2C signals, confirming that the readings are indeed correct.

Notably, no SET_CFGUPDATE() function was invoked during this sequence.

For clarity, the items referenced in the log file are explained as follows:

- wSafetyAlertA: [0x02] Safety Alert A Register

- wSafetyStatusA: [0x03] Safety Status A Register

- wBQBatteryStatus: [0x12] Battery Status Register

- OTPW: OTPW bit within the [0x12] Battery Status Register bit-field

- OTPB: OTPB bit within the [0x12] Battery Status Register bit-field

- iCell_V1 to iCell_V16: Individual cell voltage readings

- iSTACK_V: [0x34] Stack Voltage

- iPACK_V: [0x36] PACK Pin Voltage

- iLD_V: [0x38] LD Pin Voltage

- iCC2: [0x3A] CC2 Current

- iINT_T: [0x68] Internal Temperature

- iTS1_T: [0x70] TS1 Temperature

- iTS3_T: [0x74] TS3 Temperature

We appreciate your assistance in resolving this issue promptly.