Other Parts Discussed in Thread: UCD9081

Hello All,

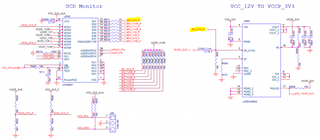

We are using LMZM33602 Power Module in our design. Please review SYNC Connectivity of the attached Schematic snippet.

LMZM33602 will be in disabled state by default because of the 10K pull-down connected to this pin. Regulator IC will be enabled by the 3.3V signal driven by UCD9081 power manager IC. LVCMOS (3.3V) 240KHz Clock generated by FPGA will be connected to EN/SYNC pin through AC Coupling capacitor. Please let us know if the schematic connection and Voltage levels will be fine for EN/SYNC feature to be used. We have also given option of Resistor divider option by placing series resistor on UCD Enable output line if the voltage generated by the UCD9081 IC needs to be reduced to meet the EN pin max voltage. Please let me know your suggestion to improve the design and for the circuit to work.