Other Parts Discussed in Thread: TLC5940

When I wrote driver software (python) for TLC59401, I have found that OUT15 LED is less brighter than other.

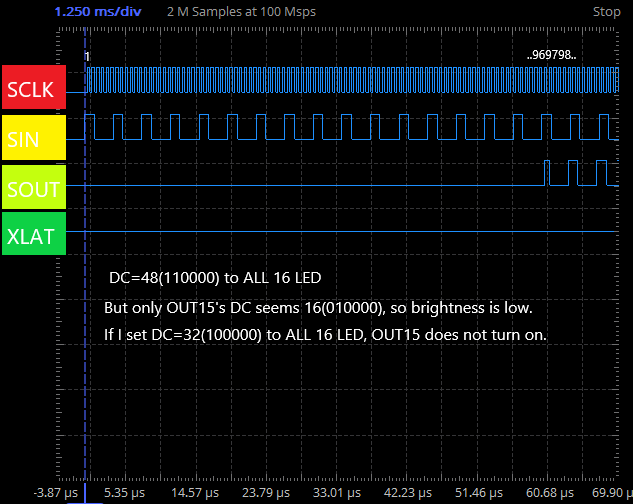

For all 16 LED, same DC and same GS value send, but only OUT15 LED is about half brightness. If I send DC=32 and any GS value, only OUT15 is not turn on.

I think TLC59401 can't receive MSB=1 of DC data.

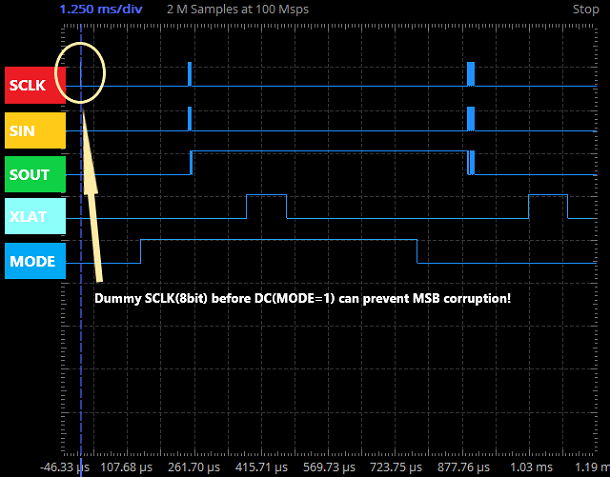

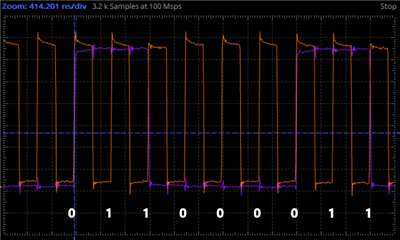

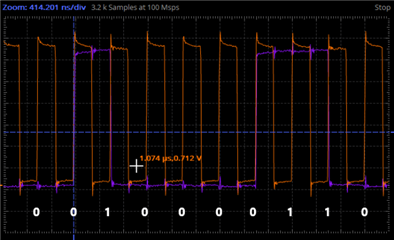

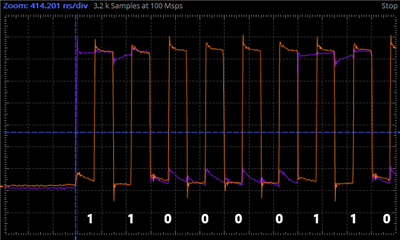

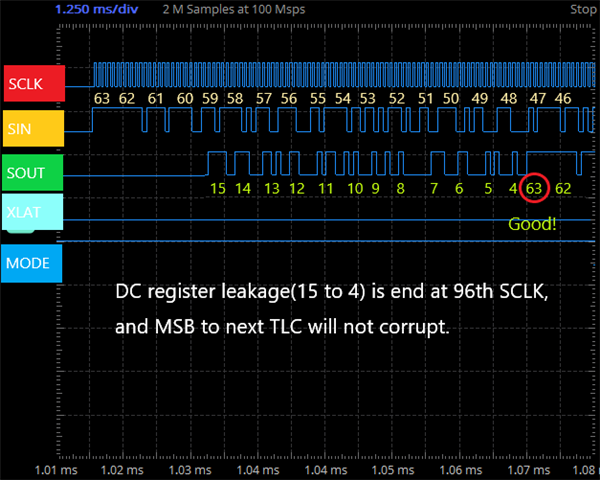

Upper chart is analyzer of SCLK/SIN/SOUT/XLAT. DC=48(110000) to 32 LED(TLC59401 is cascaded) found SIN, but MSB of SOUT seems DC=16(010000), so OUT15 on 2nd TLC59401 is less brighter than other.

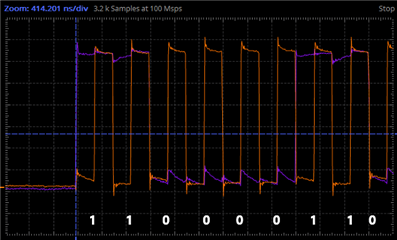

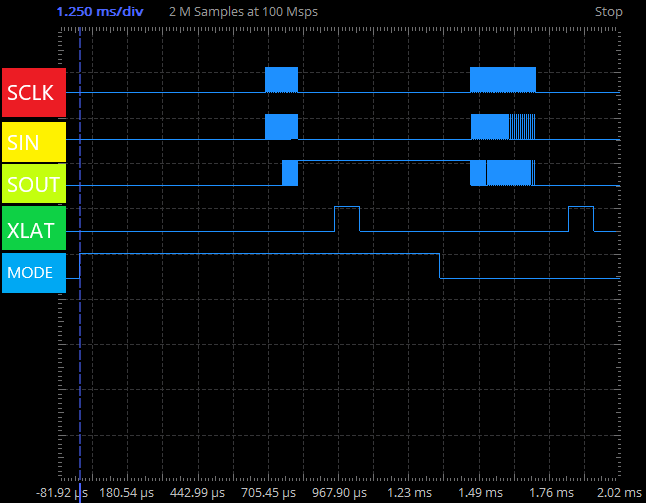

This is all signal for DC=32 and GS=32 to all 32 LED (for two TLC59401). I tried Bit Bang driver instead SPI, but result was same. This problem (MSB force to 0) is not happen in GS data, only on DC data.

If I changed SPI Mode 0 to 3, this problem disappeared. But SPI Mode 3 cause 'SCLK Idle is High', it is different to datasheet.

My LED board has four TLC59401 and 64 LED, I wrote driver software that add 96bit dummy data to top of DC data, it works fine.