Hello,

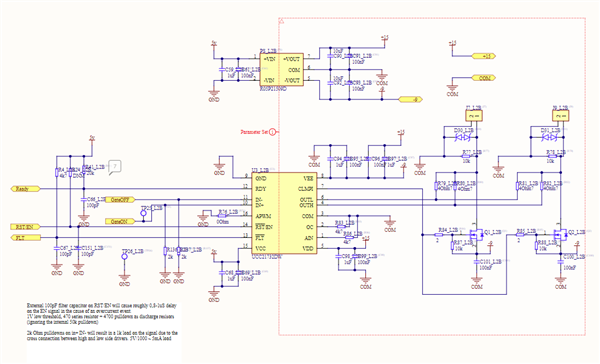

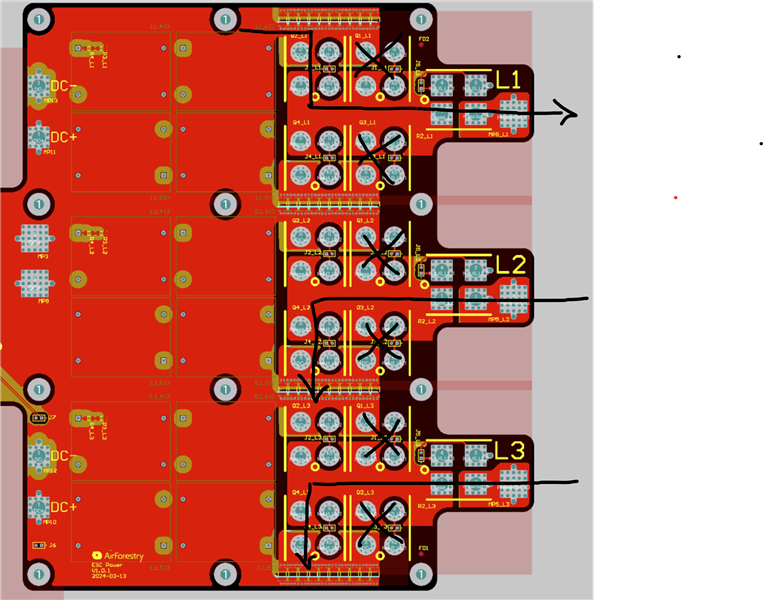

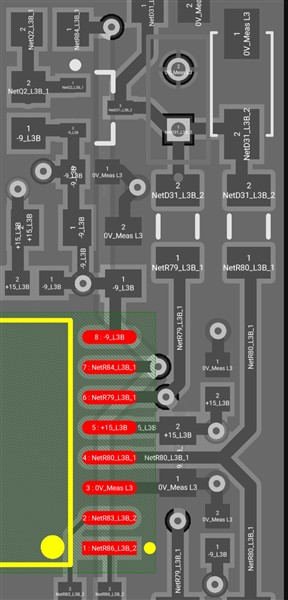

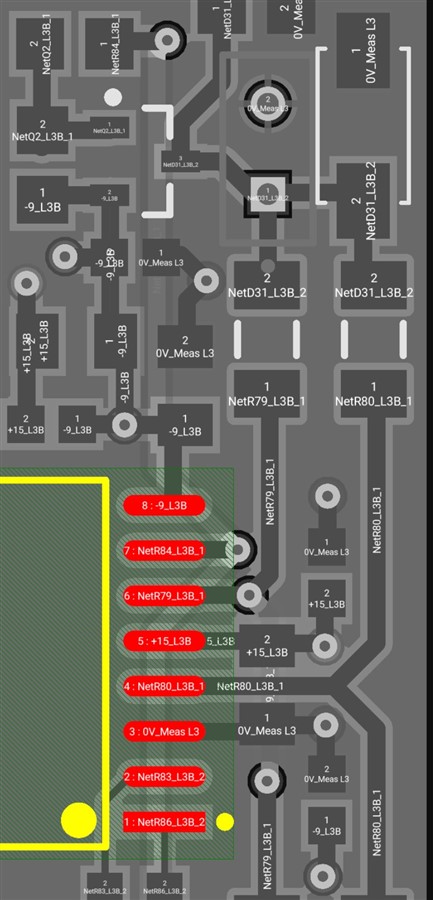

Schematic and a snapshot of the layout is added below.

We are building an inverter using the UCC21732 and having problem with the FLT-pin false triggering. Changes done compared to the schematic below is that the OC-pin and AIN have been disabled by tying them to ground via an 0 Ohm resistors at R83 and R86. Also R76 have been removed so that the APWM is now floating.

Some conclusions and things we have tried:

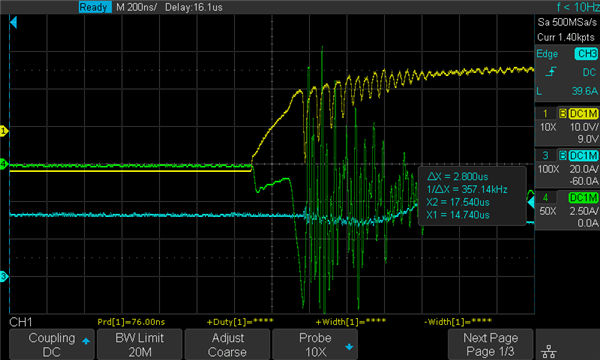

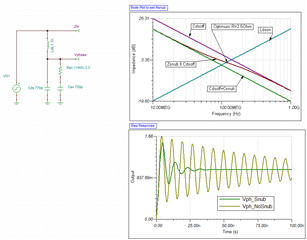

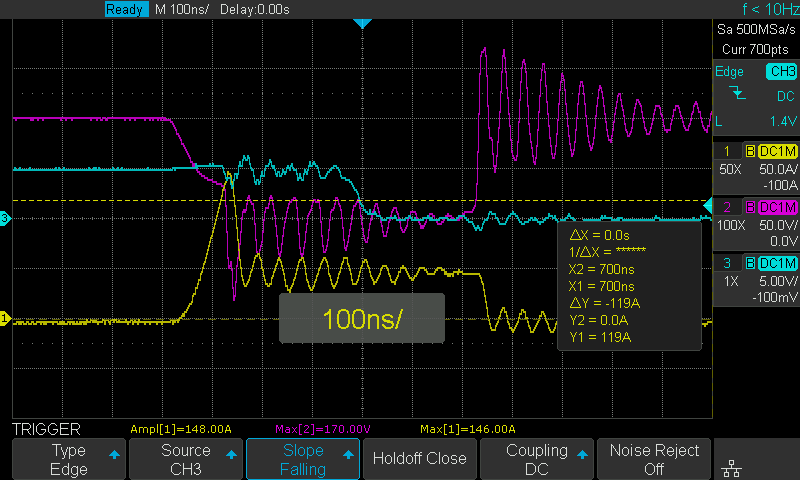

- It seems to be happening when we increase voltage to around 100V and 150 A. Decreasing the current decreases the FAULT occurence rate. Running at lower voltage more or less removes the issue. We have assumed this is due to the (by us unused) over current pin false triggering.

- We observed no oscillations on the ready pin.

- We’re having a single gate driver feeding two parallell mosfets (with separate gate resistors per mosfet) but during testing only a single mosfet is mounted.

- We’ve tried with 1 ohm gate resistors, 4.7 ohm, and 10 ohm respectively, no luck.

- It seemed like removing the miller discharge mosfets, Q1 and Q3 decreased the amount of FAULTs.

- The CLMPI pin still had the 2 Ohm and 10k to -9V.

We’ve also tried to replace the UCC21732DW with the UCC21756QDWRQ1 in order to have the desaturation pin instead. With a hope of the higher detection voltage of 5V to solve the problem, but same behavior.

The main question is why the OC-pin keeps triggering when it's supposed to be deactivated, or is it something we are missing here?

Best regards, Jimmy