Other Parts Discussed in Thread: UCC21732

Hello,

It seems like I'm getting unexpected GD_FLT tripping. I'm using this in a synchronous buck converter, and I have two phases interleaved (4 UCC21732 devices GD_FLT output connected together). I'm operating in open-loop with a fixed duty cycle, and as I increase the voltage, I get a GD_FLT. I have the OC pin directly shorted to the COM pin here.

It seems like this issues might be correlated to peak inductor current because if I double the switching frequency, I can achieve double to bus voltage. Additionally, I can operate well past the tripping voltage if I disconnect my inductor and just turn the devices on/off (no reactive current flow).

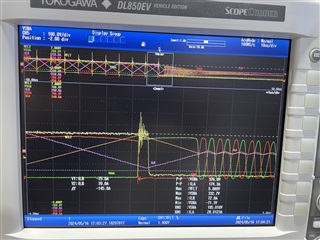

GD_FLT is CH1 (yellow)