Other Parts Discussed in Thread: UCC14141EVM-068, UCC14141-Q1

Tool/software:

Dear TI experts,

My customer now tests UCC14140-Q1 in their own PCB.

They fould that there is ripple noise in the 15V output even no load is applied.

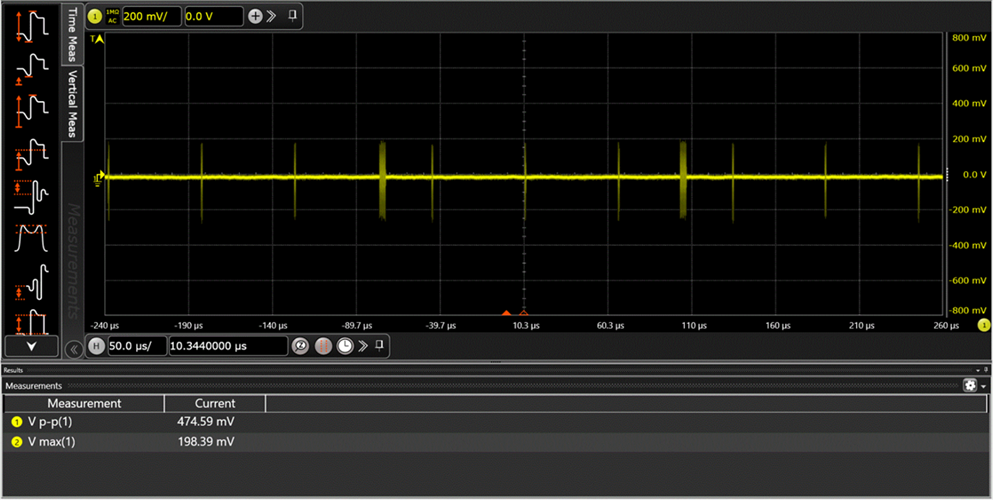

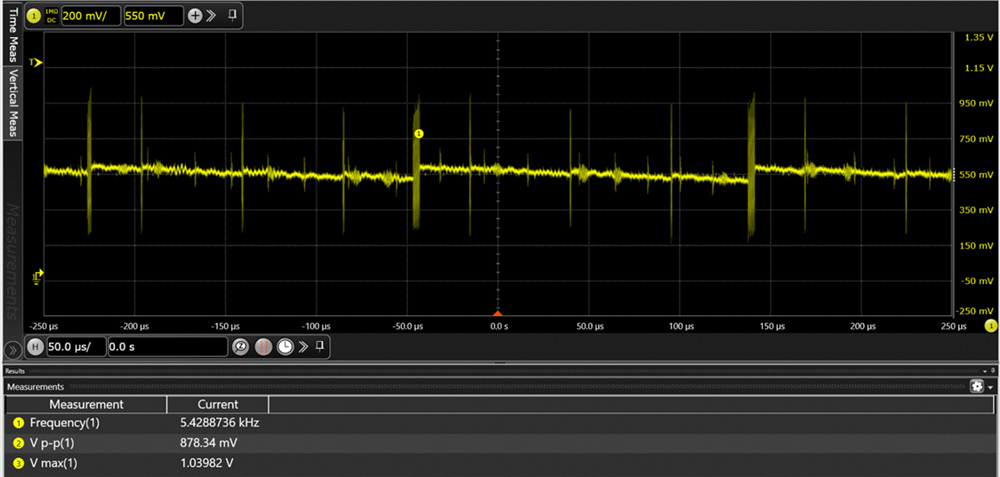

I attach the waveform of AC noise and DC noise.

1. AC noise

2. DC noise

I also attach the schematic and layout for your convenience. (they measured AC and DC noises on 15V output.)

Please review this issue, and advise me about reducing this noises.

Best regards,

Chase