Other Parts Discussed in Thread: LM74703-Q1, LM74701-Q1

Tool/software:

Hello Expert,

Could you please answer following questions?

Does EC table's FET GOOD HIGH include voltage drop at RFETGOOD or we should add voltage drop at RFETGOOD to estimate actual FET good pin output voltage?

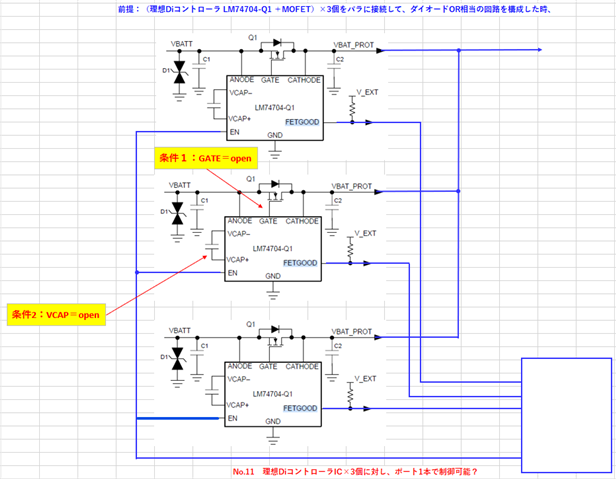

They are considering to use 3pcs LM74704-Q1 as below.

Currently their plan to use same EN signal for controlling all of LM74704-Q1.

Then could you please answer following question?

- Does FET good maintain high when any one LM74704-Q1's gate pin open if the other LM74704-Q1 work correctly?

- Does FET good become low when any one LM74704-Q1's Vcap+/- open even if the other LM74704-Q1 work correctly?

- Is there any concern by controlling all of LM74704-Q1 by one enable signal?(for example, device variation cause different FETGOOD confirmation timing from start-up event and some LM74704-Q1 detect wrong Anode to cathode short, Continuous enable high for FETGOOD=Low device some time cause wrong turn on and cause damage, etc...)

Best regards,

Kazuki Kuramochi