Other Parts Discussed in Thread: LM74700-Q1, LM74722-Q1, LM74910-Q1

Tool/software:

Hi Team,

My customer would like to parallel three FETs to support 100A application.

May I learn from you how to know driving capability for FET?

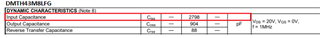

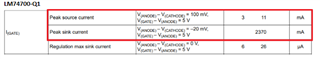

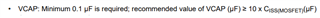

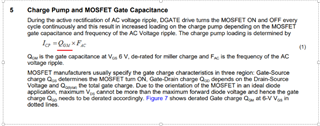

Customer use PSMN2R3-100SSE*3 for 8~48Vin/100A, besides FET at on status, I also worry about turn on/off.

BTW, I have check excel sheet and driving current from datasheet. But would like to learn more from you.

Regards,

Ben