Tool/software:

Dear Team,

I hope this message finds you well!

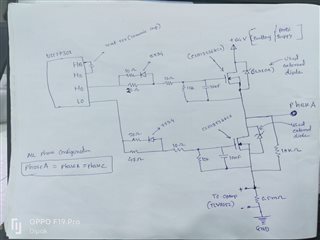

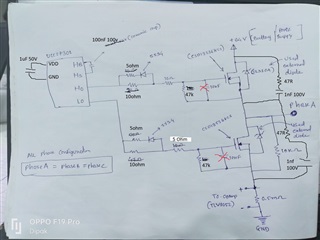

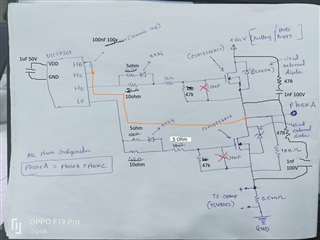

We are currently working on the design of a 3KW BLDC controller board and have implemented the UCC27301 gate driver along with the CSD19536CKS MOSFET. However, we are encountering some challenges related to the MOSFET’s rising and falling edges.

I have attached the configuration details for our gate driver as well as an image showing the MOSFET ringing.

We would greatly appreciate it if you could review the attached schematic and waveform and provide us with guidance on how to resolve these issues.

Additionally, we have observed that when the duty cycle is set to full (running at 15.6kHz), the gate driver output drops to zero instead of reaching the maximum value.

Any insights on this matter would also be very helpful.

Thank you very much for your assistance.

Best regards,

Dipak