Tool/software:

Dear master.

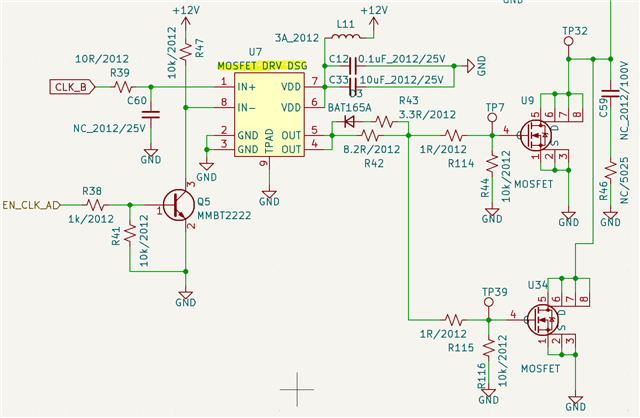

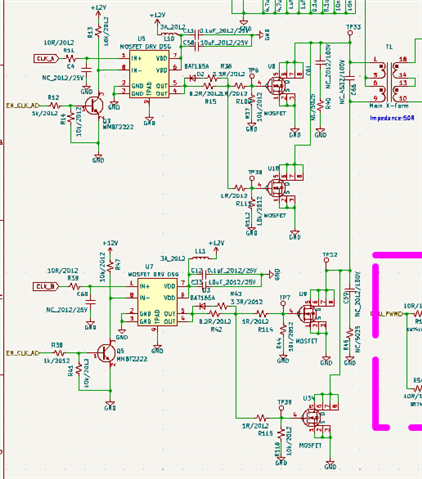

I'm using UCC27614 8pin SON DSG Package.

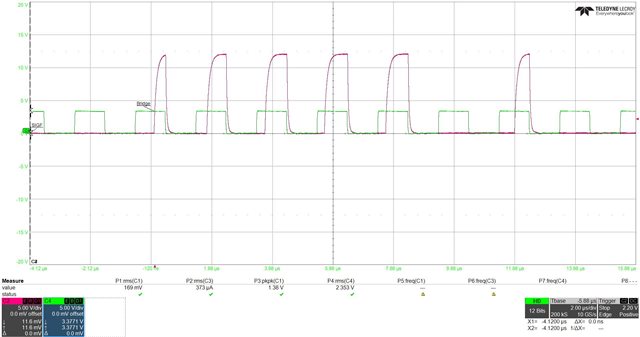

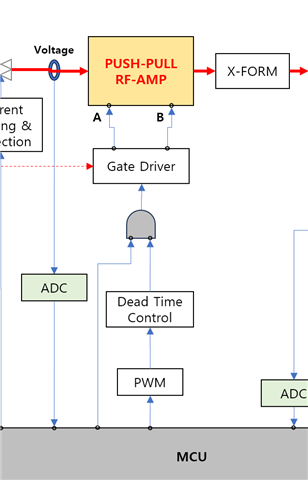

■ UCC27614 Operating Condition.

- Operating Freq. : 500kHz / 300kHz.

- FET : BSC146N10LS5 parallel driving.

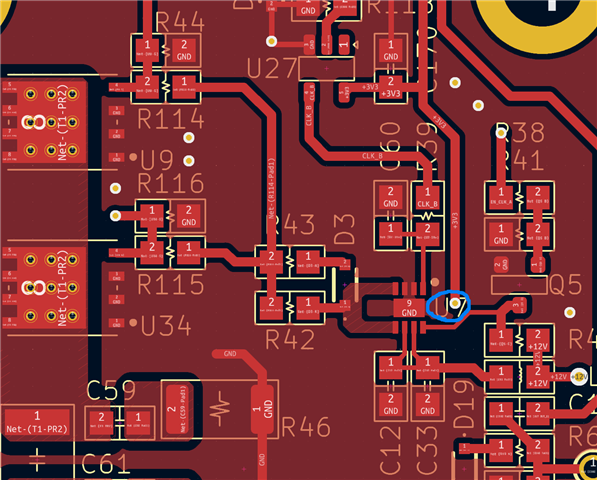

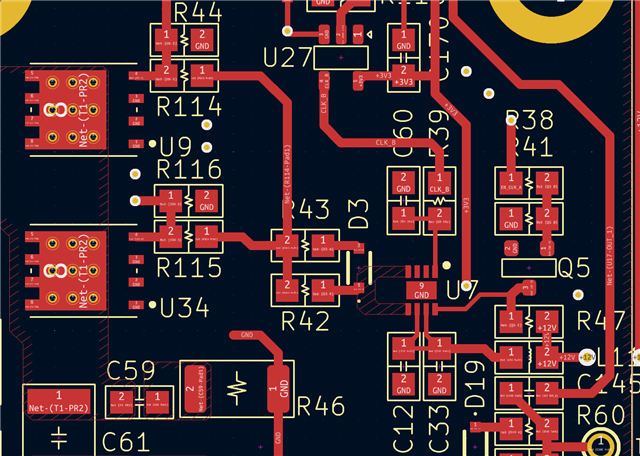

- Schematic & pattern : See below.

- 1.6T 2 layer PCB.

-Trouble : 1 PCB is out of order.

1 PCB has operating abnormal operation.

Can you advise to me what's wrong?