Other Parts Discussed in Thread: , , TPS65987D, TPS65981, TPS65987

Tool/software:

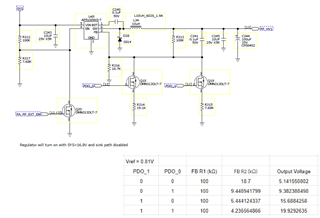

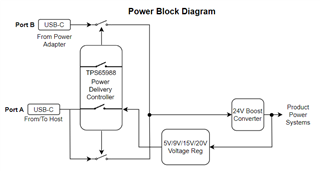

Our system is made the same as in the TPS65988DKEVM reference:

| GPIO12 | GPIO13 | Src Voltage |

| 0 | 0 | 5 |

| 1 | 0 | 9 |

| 0 | 1 | 15 |

| 1 | 1 | 20 |

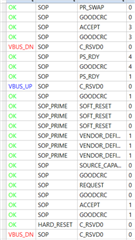

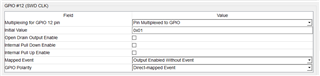

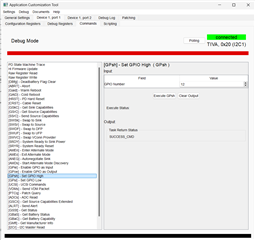

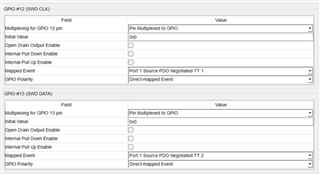

We were ablwe to get all functions working properly with the EVK. We could source all 4 voltages to port A. Our design however is using the TPS65988DH. I translated the parameters from the TPS65988DK based .pjt file to the TPS65988DH .pjt file as best I could. Here is the setting for GPIO 12 for the TPS65988DK

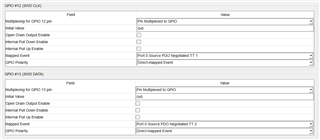

The closest setting I could get for the TPS65988DH is the following:

I assumed that Port A is reffered to as Port 0 on the TPS65988DH and Port 1 on the TPS65988DK.

GPIO12 is not going high for 9V or 20V. GPIO13 is working properly and is going high for 15V and 20V.

Attached is the .pjt file I am working with.

ASrc5VonlyBExtSw-1.19MaxSrc_TTExp.pjt