- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

Q1. The circuit breaker threshold I(CB)

The description of the operation for TJ<[T(TSD)-10℃] differs depending on the item in the data sheet.

There is a difference in the notation of the period during which TJ<[T(TSD)-10℃] falls to low, being 512[ms] and 540[ms], but which is correct?

Q2. Recommended value of COUT

The data sheet does not state how to determine the recommended value of COUT. How should I determine it?

Also, C5 (electrolytic capacitor) is placed in the EVM, but is it necessary to place C5 when filtering low-frequency noise?

Q3. Internal block diagram

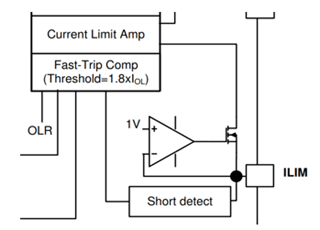

A. When the ILIM pin voltage falls below 1V, the FET is turned on and a short is detected.

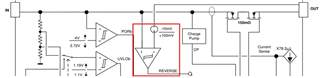

B. This is a comparator for detecting reverse input voltage. When the input voltage falls below -10[mV], it outputs Low, and when it exceeds 100[mV], it outputs High.

Regarding the internal block diagram, is my understanding of A and B correct?

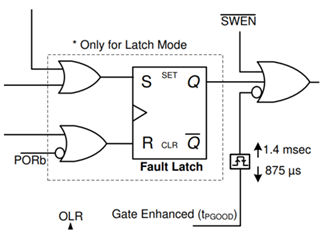

Also, the data sheet states that it is designed to eliminate erroneous signals using a "de-glitch." Is the following a correct "de-glitch circuit"?

Could you please briefly explain how it works?

Q4. Current Monitoring

Is the output range of IMON "1.5V/A" correct? Also, which formula should I use when designing R(IMON)? Could you please briefly explain the two formulas?

Q5. Fault response

When overloaded, FLTb drops to low, but Vout may remain output.

When Vin is increased, the following occurs when Vin: 34.95 [V] / ILOAD: 2.24 [A]. Is this behavior normal?

Thanks,

Conor

Hello Conor,

Q1: 512 mS retry delay in case of thermal shut down. 540mS is retry delay during CB mode.

Q2: There is not recommended value. It usually depends on the end application. To reduce the risk of negative spike due to parasitic inductance min cap of 0.1uF or higher can be placed at output.

Q3: Yes, your understanding is correct.

Q4: Both are correct. You can use the second one for simplicity if your input voltage is more that 5.5V.

Q5:Is this waveform in datasheet ? This looks to be device is in current limit mode. Limiting the current to 2.23A before it goes to auto retry.

/FLT asserts when device goes into current limit. That's why you are seeing red LED.

Thanks

Amrit

Hi Amrit,

Thank you for your reply.

The following 2 questions haven't been answered so could you please give your opinion?

Also, the data sheet states that it is designed to eliminate erroneous signals using a "de-glitch." Is the following a correct "de-glitch circuit"?

Could you please briefly explain how it works?

Could you please briefly explain the two formulas?

No, this is the waveform measured by EVM.

Vout continues to be output after FLT is asserted low. Is this normal behavior?

Q5:Is this waveform in datasheet ?

Thanks,

Conor

Hello Conor,

Q1:Check the "9.3.5.3 FAULT Response" section from datasheet for working of PGOOD de-glitch circuit. It's to provide a time delay before asset the PGOOD which is used to enable downstream DC-DC.

Q2: Both the formulas are same. Please use the second formula which is generic and simplified.

Thanks

Amrit

Hi Amrit,

Thank you for your reply. What about the following?

No, this is the waveform measured by EVM.

Vout continues to be output after FLT is asserted low. Is this normal behavior?

Thanks,

Conor

Hello Conor,

Already replied in my first answer.

Pasting the same.

This looks to be device is in current limit mode. Limiting the current to 2.23A before it goes to auto retry.

/FLT asserts when device goes into current limit. That's why you are seeing red LED and VOUT is still there.

Thanks

Hi Amrit,

Already replied in my first answer.

OK, I would like to confirm that the following is correct.

1. In current limit mode, FLT is asserted LOW.

2. Vout continues to be output until the junction temperature reaches the thermal shutdown threshold (T(TSD)).

3. The thermal shutdown threshold is exceeded and the internal FET is turned off.

4. An automatic retry cycle begins after 512 ms.

Thanks,

Conor