Tool/software:

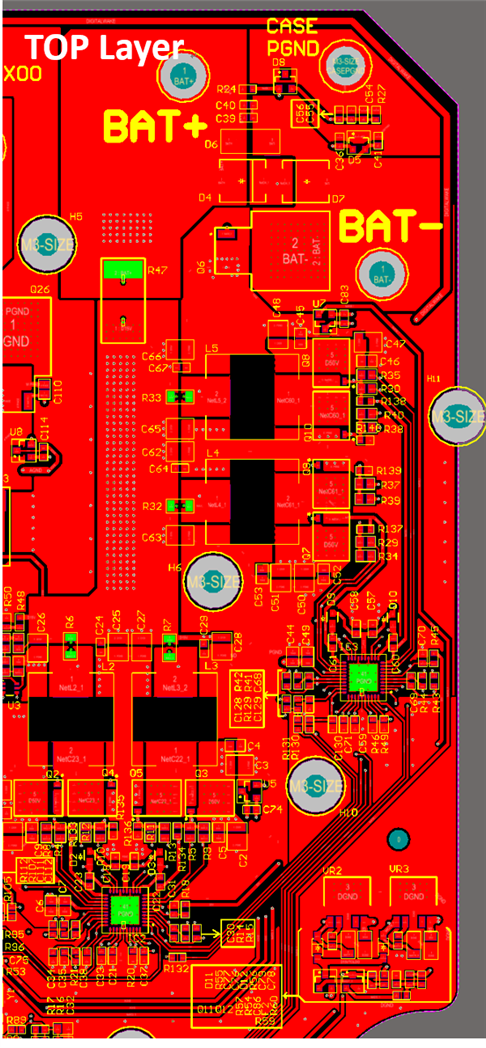

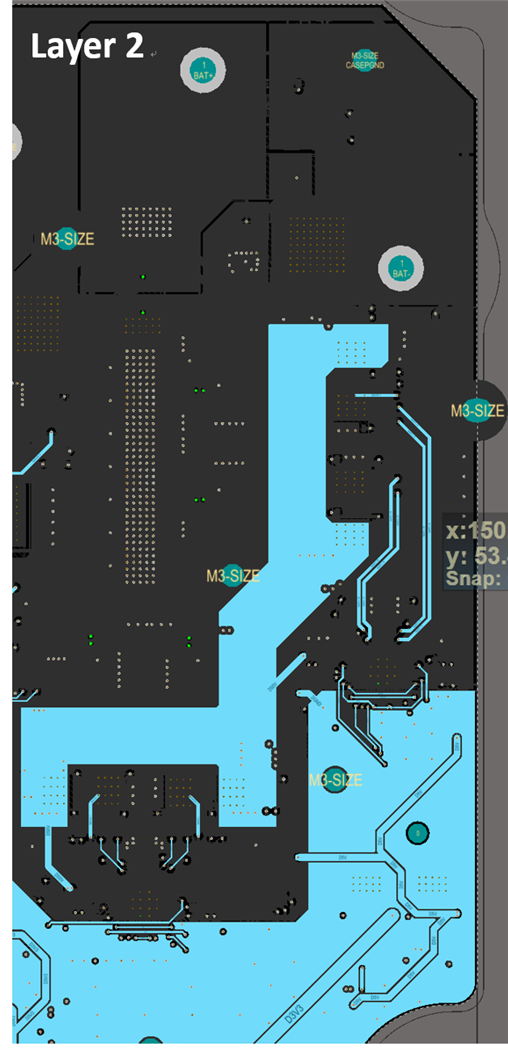

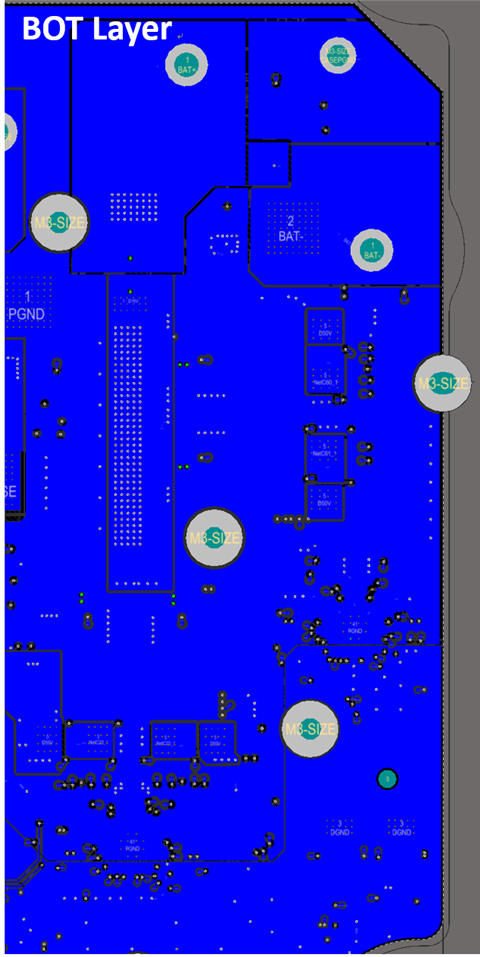

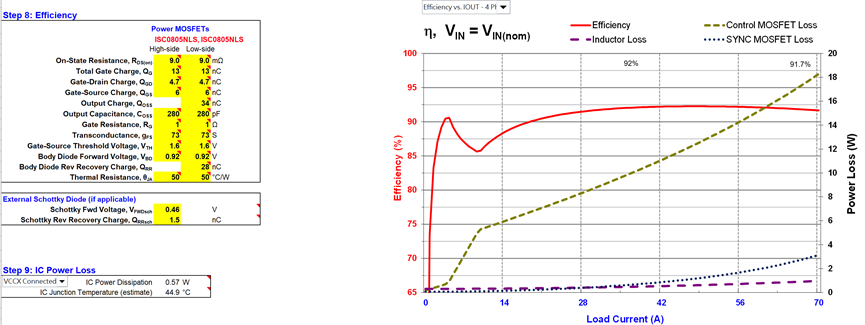

Using the 4-phase synchronous buck configuration,

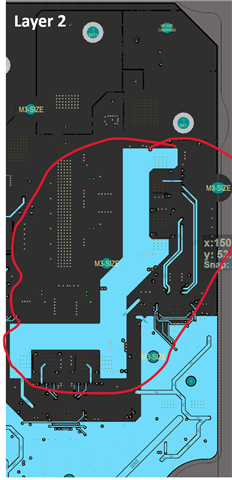

Please find the schematic and quickstart design below.

LM5143A-Q1 Quickstart Design.pdf

we observed the following:

In DEM mode with Vin = 50 V, Vout = 15 V, and output current of 10 A, we observed that most of the current flows through Phase 2, resulting in its temperature being about 20 °C higher than the other phases. Meanwhile, the temperatures of Phases 3 and 4 are lower, indicating that the current distribution is not balanced.

Could you please advise how to improve the design so that the current is evenly shared across the four phases?

Best regards,

YUMING