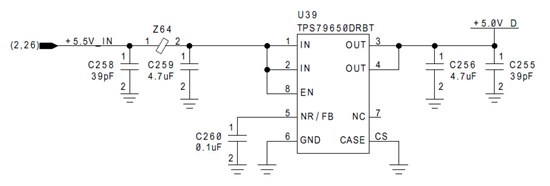

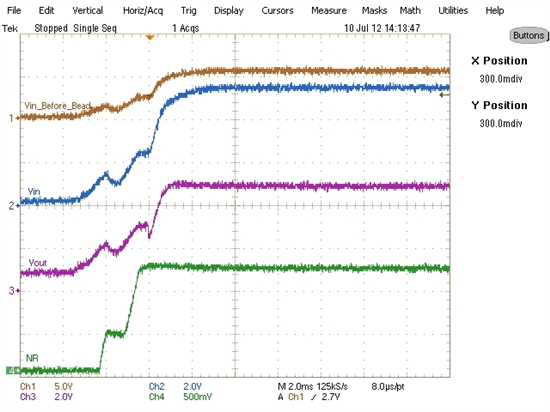

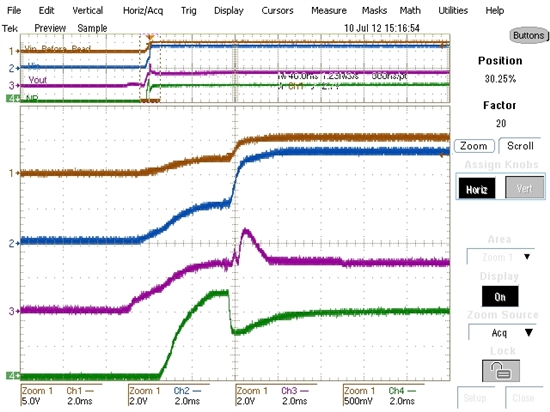

We are using two LDO's in our design: TPS79650 and TPS71733. When testing at temperature of +70C ambient (with approximately 10-15C internal temp rise) we are seeing these devices lock-up while power-cycling. Symptom is reference appears to go to 0.8V instead of 1.2V as monitored on the noise reduction pin.

The block diagrams of the TPS71733 datasheet show a selection circuit between a high and low reference voltage based on a Vout of 1.6V. The TPS79650 block diagram does not show this circuit but it appears it also has this function based on the failure effects. Can TI please provide details on this function and how the decision between the two references is made? This would include timing of the decision and inputs. I would like to know if further reduction or removal of the noise reduction capacitor can help address this issue by speeding up start-up time.