On released TPS65381 chip, Analog MUX output scaling does not follow the divider ratio shown in table 4-3 of the Datasheet dated Dec 13 2013

Reading that we see on our board are as follows:

|

|

Voltage |

Divider ratio |

Scaled Expected |

Hex |

Apparent readings |

Actual DIAG |

Error vs Expected |

Apparent divider ratio |

|

|

(V) |

|

(V) |

|

(V) |

(V) |

|

|

|

VDD5 |

5.02 |

2 |

2.50 |

855 |

2.604 |

2.72 |

4.15% |

1.93 |

|

VDD6 |

5.85 |

3 |

1.95 |

71e |

2.224 |

2.35 |

14.06% |

2.63 |

|

VCP |

16.7 |

13.5 |

1.24 |

6bc |

2.104 |

2.4 |

70.12% |

7.94 |

|

VSFB1 |

Pull-down |

4 |

1.23 |

3f2 |

1.233 |

1.45 |

0.56% |

|

|

VBAT_SAFING |

10.01 |

10 |

1.00 |

700 |

2.188 |

2.55 |

118.75% |

4.58 |

|

VBAT |

10.01 |

10 |

1.00 |

6d5 |

2.135 |

2.5 |

113.50% |

4.69 |

|

BG |

1.226 |

1 |

1.23 |

7bb |

2.416 |

2.5 |

97.04% |

0.51 |

|

VMBG |

1.226 |

1 |

1.23 |

7cf |

2.440 |

2.5 |

99.04% |

0.50 |

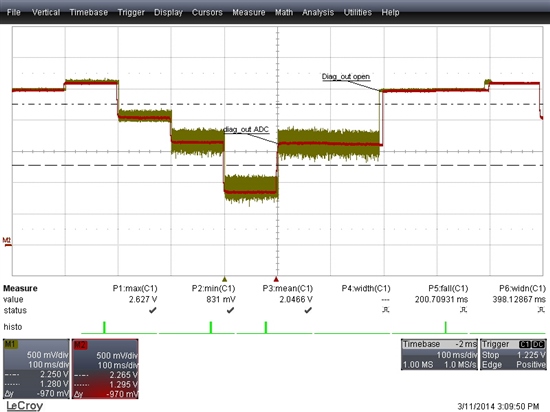

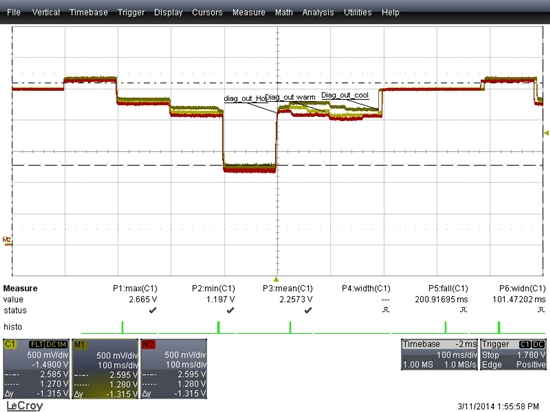

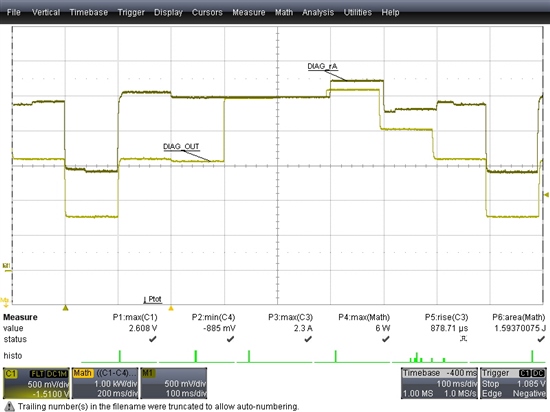

DIAG_OUT pin of TPS65381 is connected to ADC input of Hercules processor RM48L952ZWT though 1k resistor, with 2x 10nf of capacitance.

Channels on analog MUX switch state every 100ms, and settle in <5ms for each channel. ADC is sampled 90ms after the MUX switch.

Chip REV_ID register shows 0x30 while datasheet states it should be 0x31.

Is there an updated datasheet or any info on actual scaling factors?