Dear TI

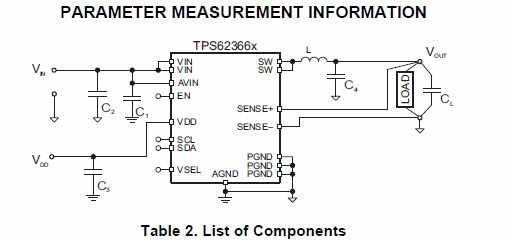

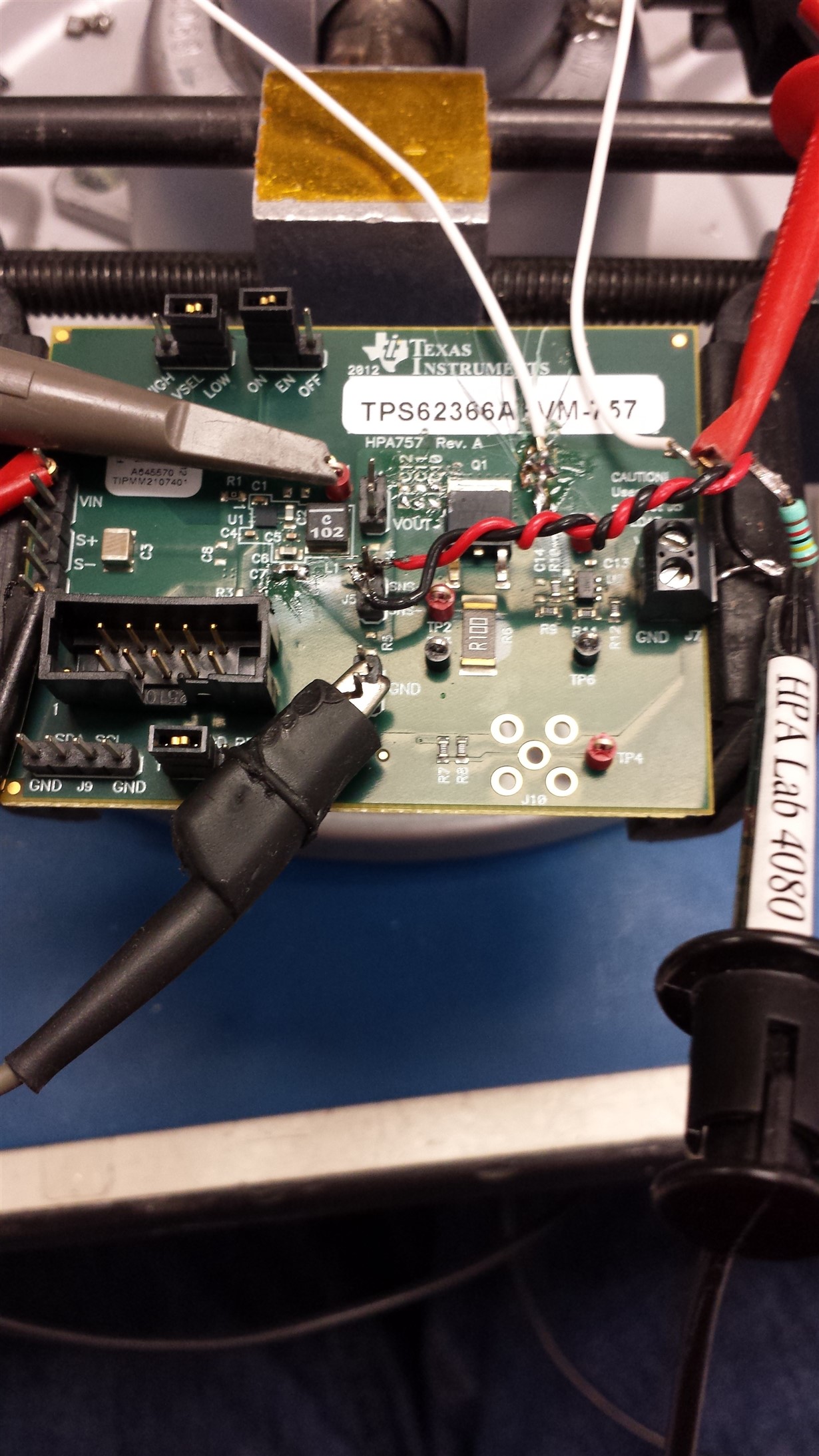

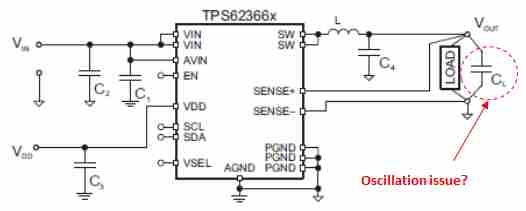

I would like to confirm an oscillation issue on web EVM of TPS62366.

I tried to move capacitor pisition with adding line inductor.

When added Cload on EVM, output was oscillating.

Please take a look attaching file.

But Cload is described on datasheet page 34 OUTPUT FILTER DESIGN Figure 51.

I'd like to know how to consider Cload. And why was Cload no good in my test on EVM?

TPS62366_oscillation_issue.pdf

Thank you and best regards

K.Narisawa