Hi,

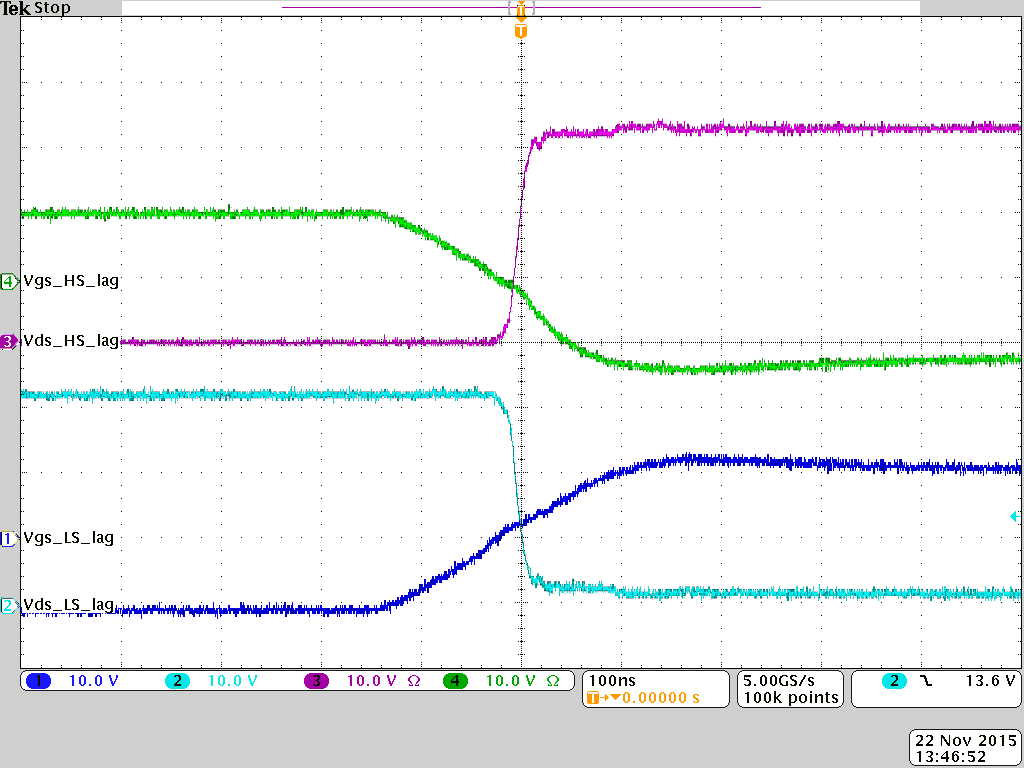

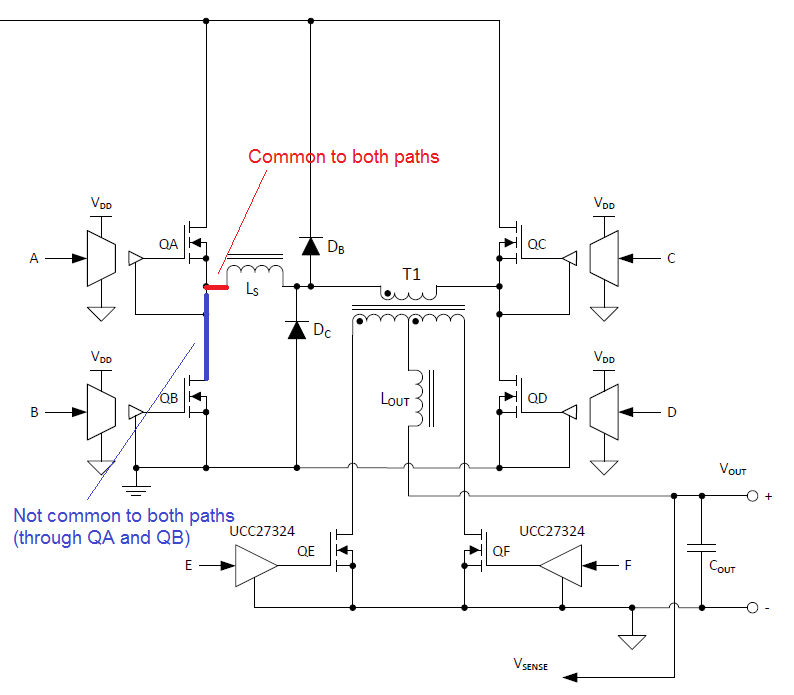

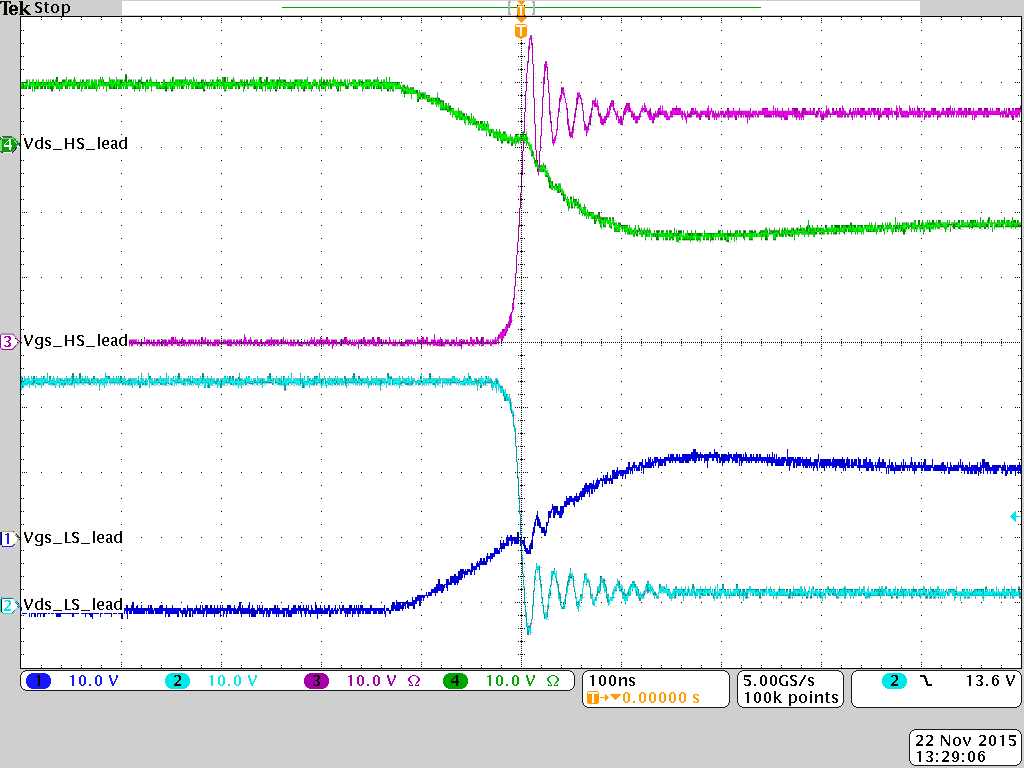

I posed this question in an earlier post, however now I have better plots and maybe someone could help me. I designed a PS ZVS converter and the leading leg has some ringing on Vds which is ousted for the lagging leg. Does anyone know due to what factors I got this behavior. Is it normal (Vds drops before Vgs rise)?  Currently the Tdelay is similar for the two legs but I believe this shall not affect the functionality.

Currently the Tdelay is similar for the two legs but I believe this shall not affect the functionality.

I the previous post I have asked also about some oscillation due to compensation loop. It proved that the Rsum was to high and the current compensation was not effective (maybe it helps).