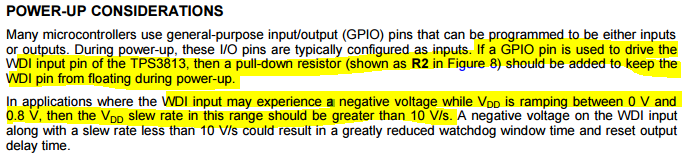

We have an application that is utilizing the TPS3813 watchdog. We had a failure of the unit that is undergoing scrutiny trying to identify the root cause. One of the possible failure paths is with the TPS3813. A few lines in the TPS3813 datasheet got us questioning our design and possible cause of failure (see highlight images below).

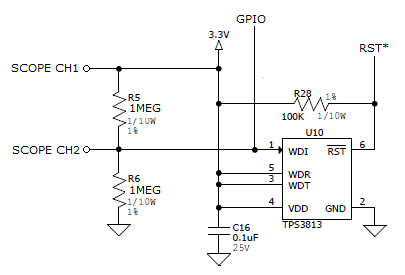

In our circuit design, the TPS3813 WDI pin does not have an external pull-up or pull-down resistor. The pin is connected directly to a GPIO pin. The GPIO pin does have an internal pull-up resistor that is hardware enabled on MPU reset. We were then questioning if the GPIO internal pull-up resistor would be active immediately on power-up or if some delay occurred before the internal pull-up became active. To test this we wired in a voltage divider on the WDI pin consisting of 1 Megaohm legs. The point of the voltage divider is to coerce the WDI pin into an invalid logic state so we can scope it. The resistance of the voltage divider legs was chosen such that the GPIO pin’s internal pull-up resistor can easily overdrive them should it be active. The test schematic is shown below.

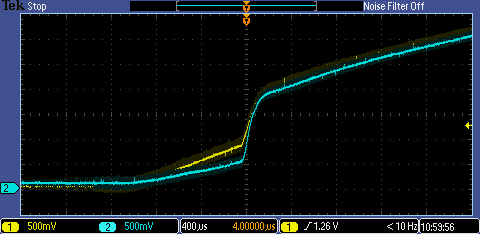

We then scoped the VDD rail and the WDI pin on power up. The scope traces are shown below. The yellow trace is the VDD rail and the blue trace is the WDI pin. The scope trace shows that the GPIO pin’s pull-up resistor does not become active until the VDD rail exceeds ~0.8 V at which point the WDI pin is pulled to VDD rail. Below ~0.8 V the WDI pin could be potentially floating.

Here are the questions we need answers to:

(1) What impact does a floating WDI on power-up have on the operation of the watchdog, the datasheet does not say? Can it cause the reset pin to be asserted low even when a valid pulse train is being applied to the watchdog after power-up?

(2) If it can be asserted low (per question 1 above), what voltages on WDI would be needed to cause this to happen? Is this a very repeatable event or a very rare event? We haven’t been able to reproduce the failure so probabilities would be useful.

(3) The datasheet specifies a pull-down resistor, while our circuit utilizes a pull-up resistor. Is this a potential issue and why?

(4) The GPIO pin’s pull-up resistor appears not to be active until VDD reaches ~0.8 V. Is this an issue?

(5) The datasheet also warns about negative transitions on WDI with a VDD slew rate of less than 10 V/s. The scope plot shows that our circuit ramp rate is much higher than that. Are there any issues here that we are missing?

Thanks