Other Parts Discussed in Thread: CSD18504KCS,

Hello,

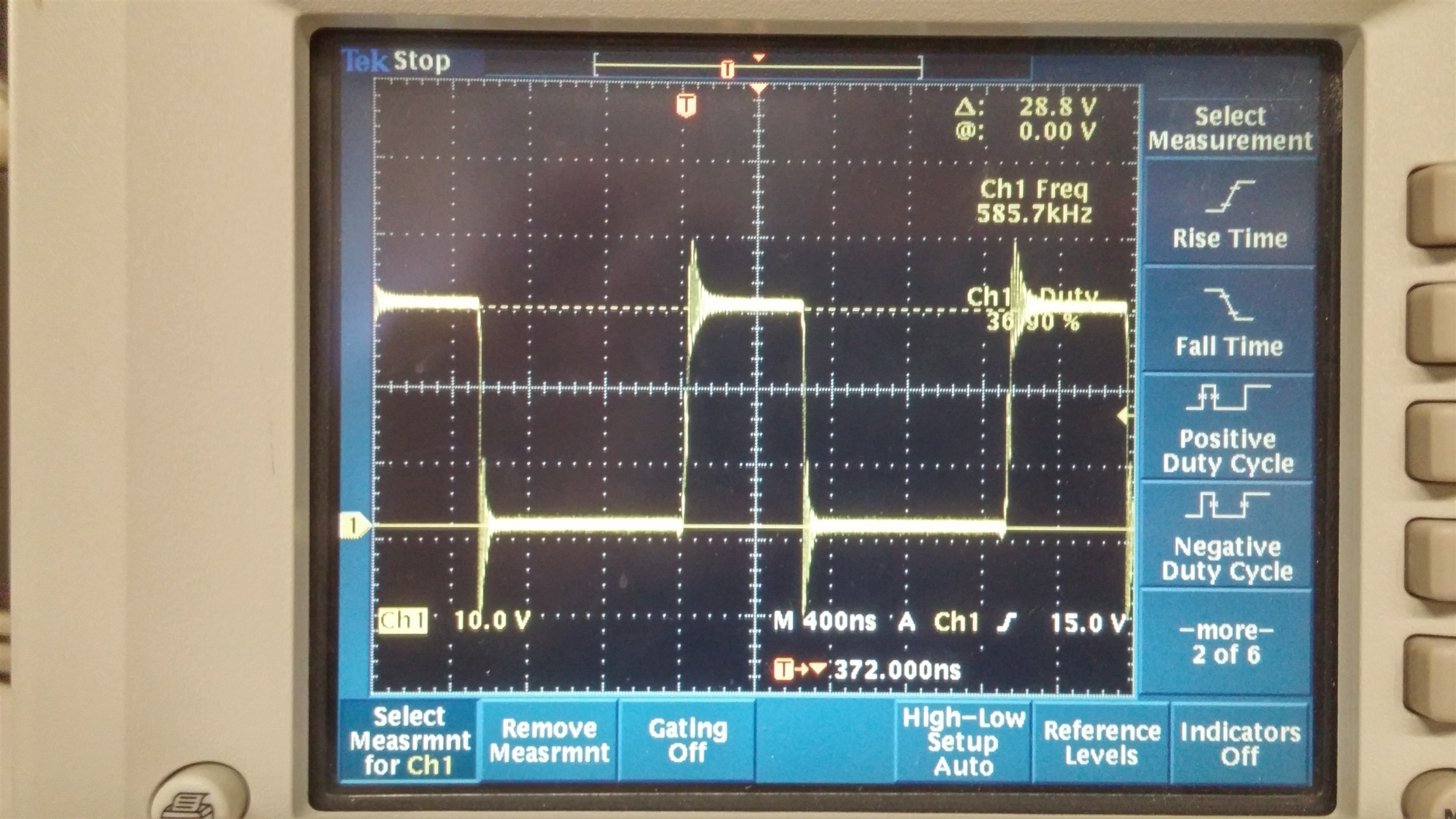

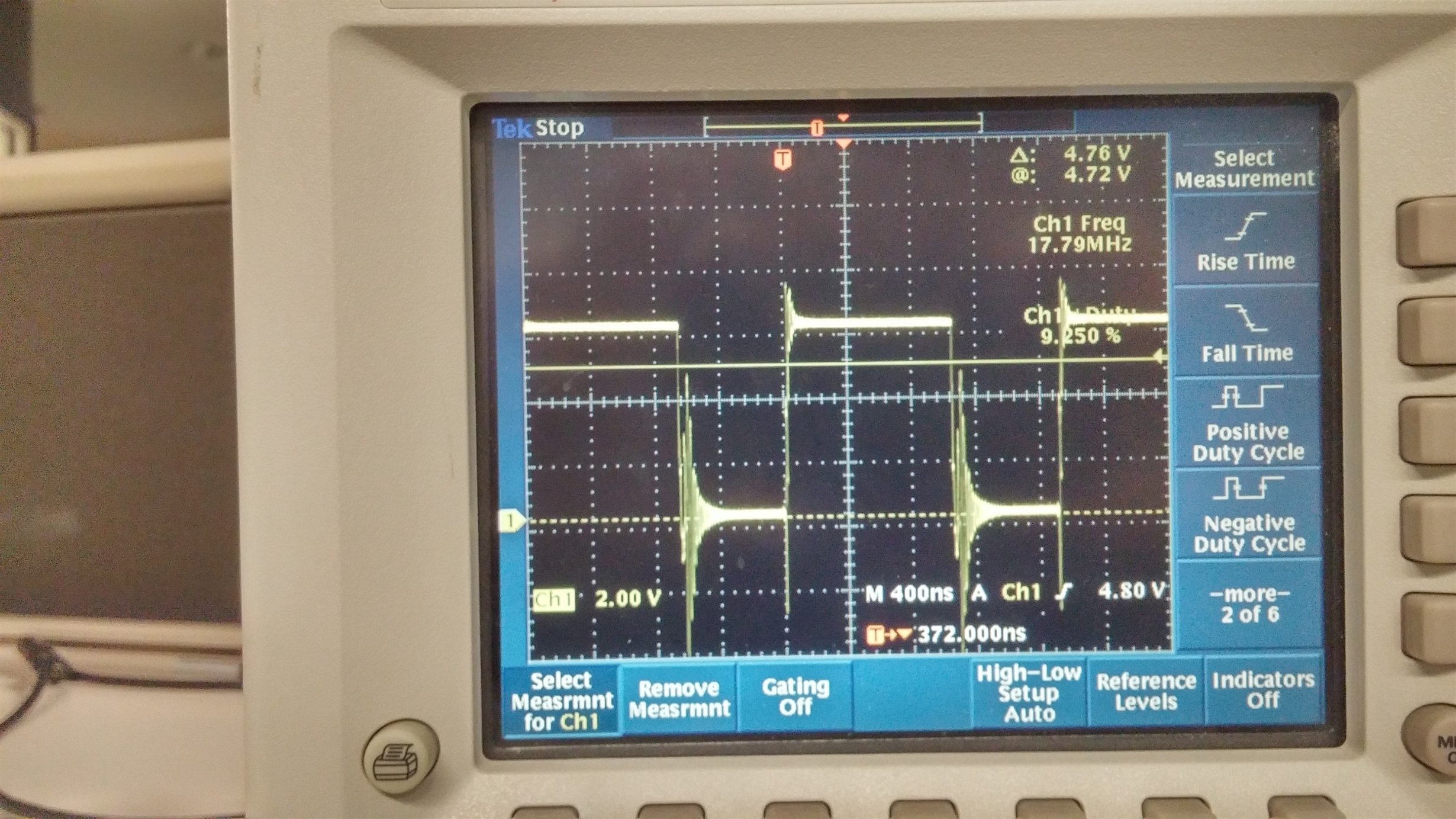

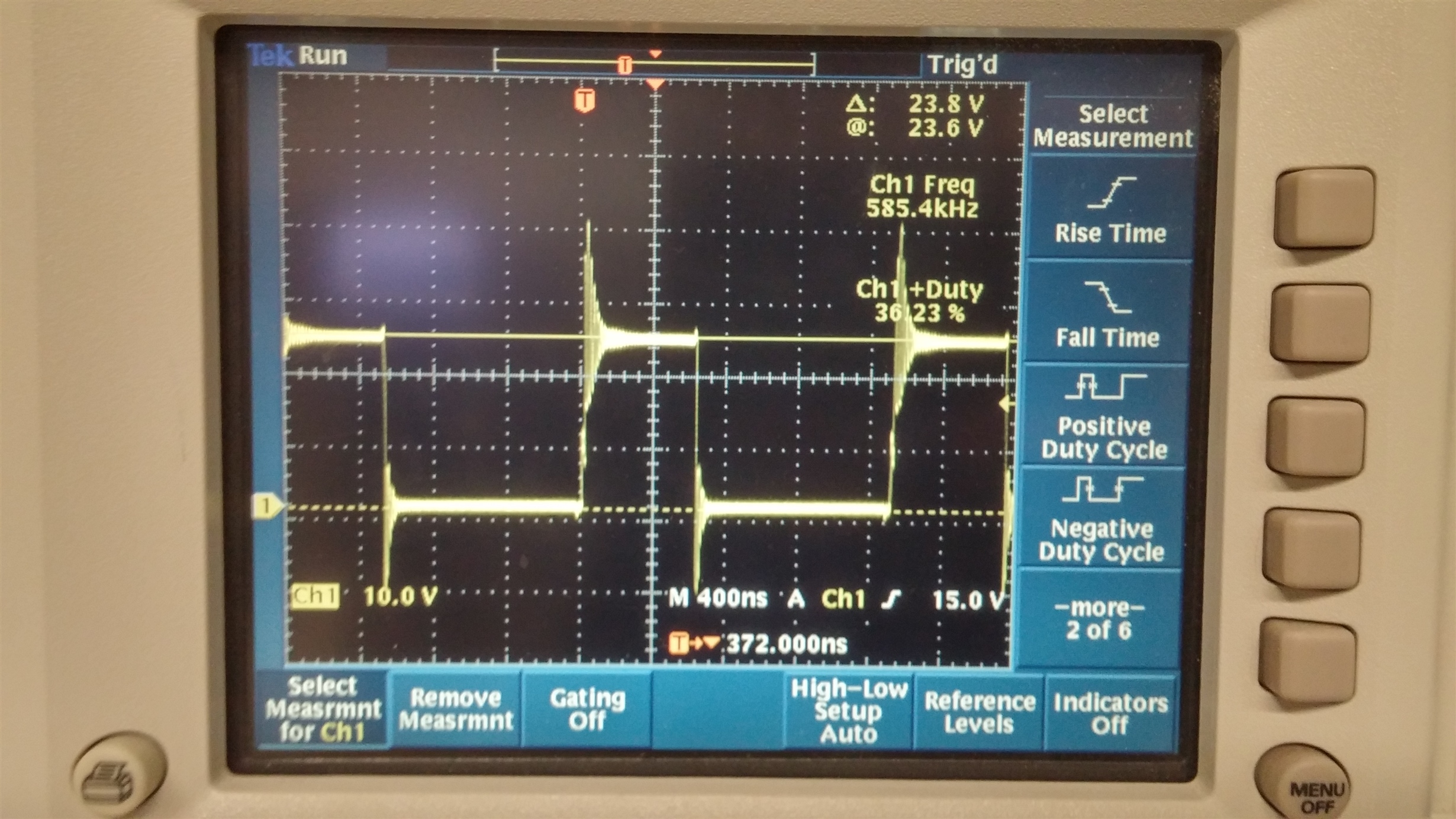

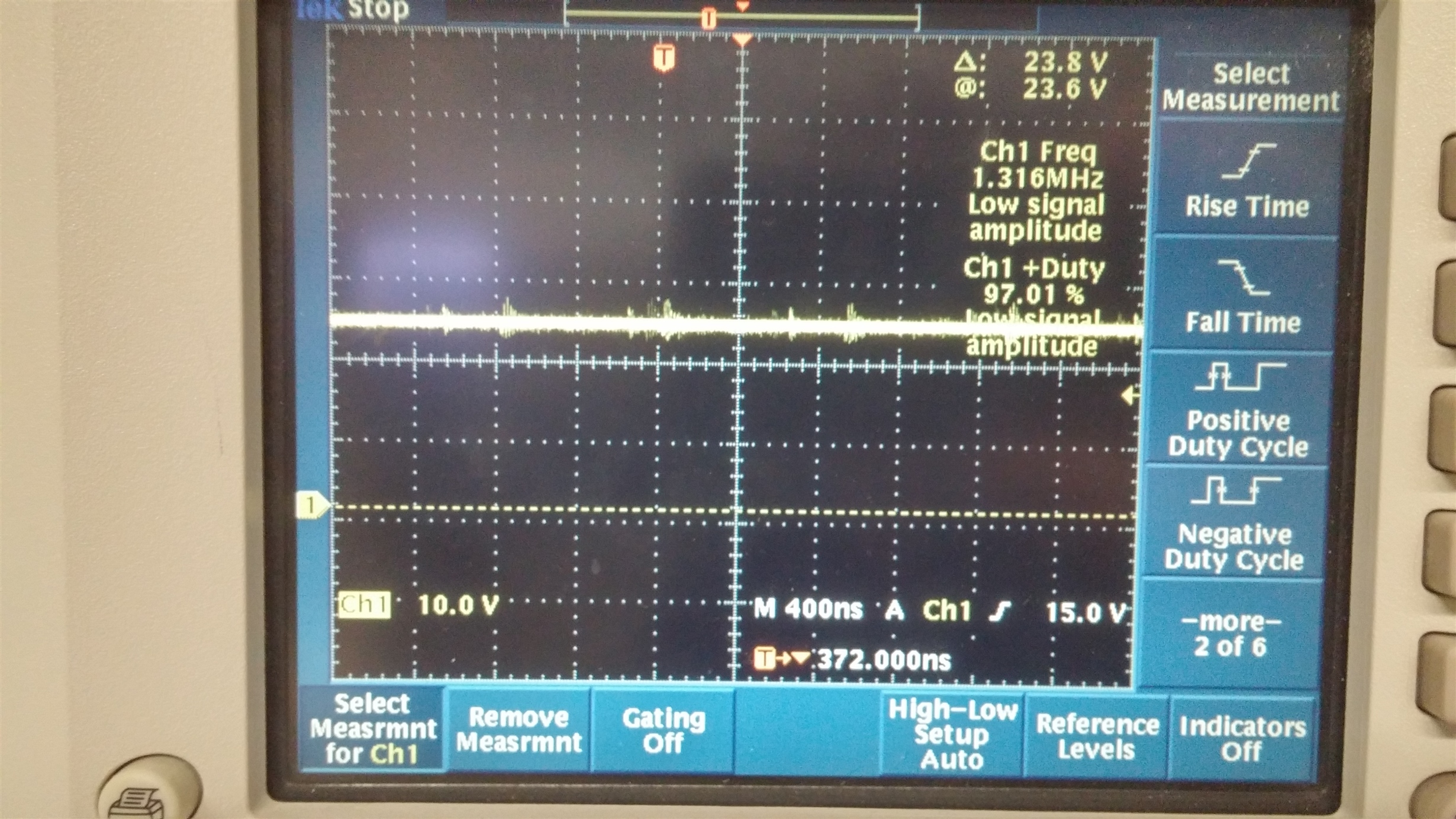

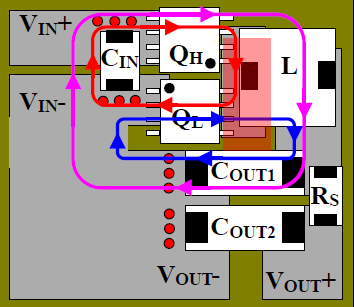

We are using a BQ24610 to charge out 8.4V 20Ah battery. We are using a 24V input supply as the power source and the battery charge current is 9A. We have had issues with very high temperature rises on the output fets attached to the Hi and Low side driver, particularly the high side. Over the 2 hours or so the battery is in constant current mode the fets can rise as much as 100C or more from room temp. Current our fets are CSD18504KCS next fets with a 6225B-MTG heatsink attached to them.

I did a little math for resistive and switching loses and I get something like 5W to 8W worst case however we measure a loss of around 14W to 16W for the battery charger. I guess I must be missing something and I was hoping you could point me in the right direction.

A copy of my schematic for this circuit is attached.SCHEMATIC1 _ 07 BATTERY CHARGER.pdf

Thanks,

John